Арифметическое устройство для работы с целыми числами с многократно увеличенной точностью

Формула / Реферат

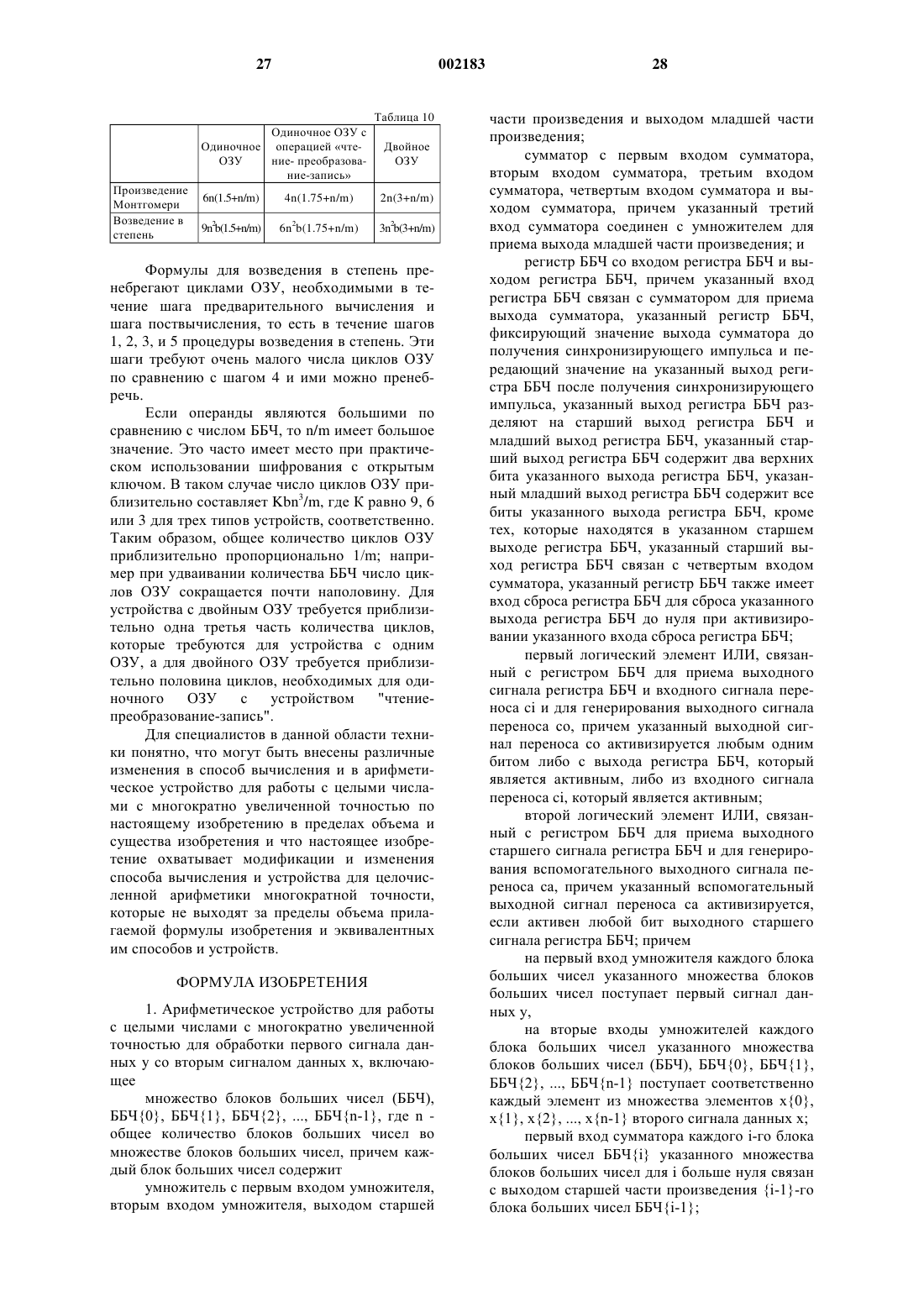

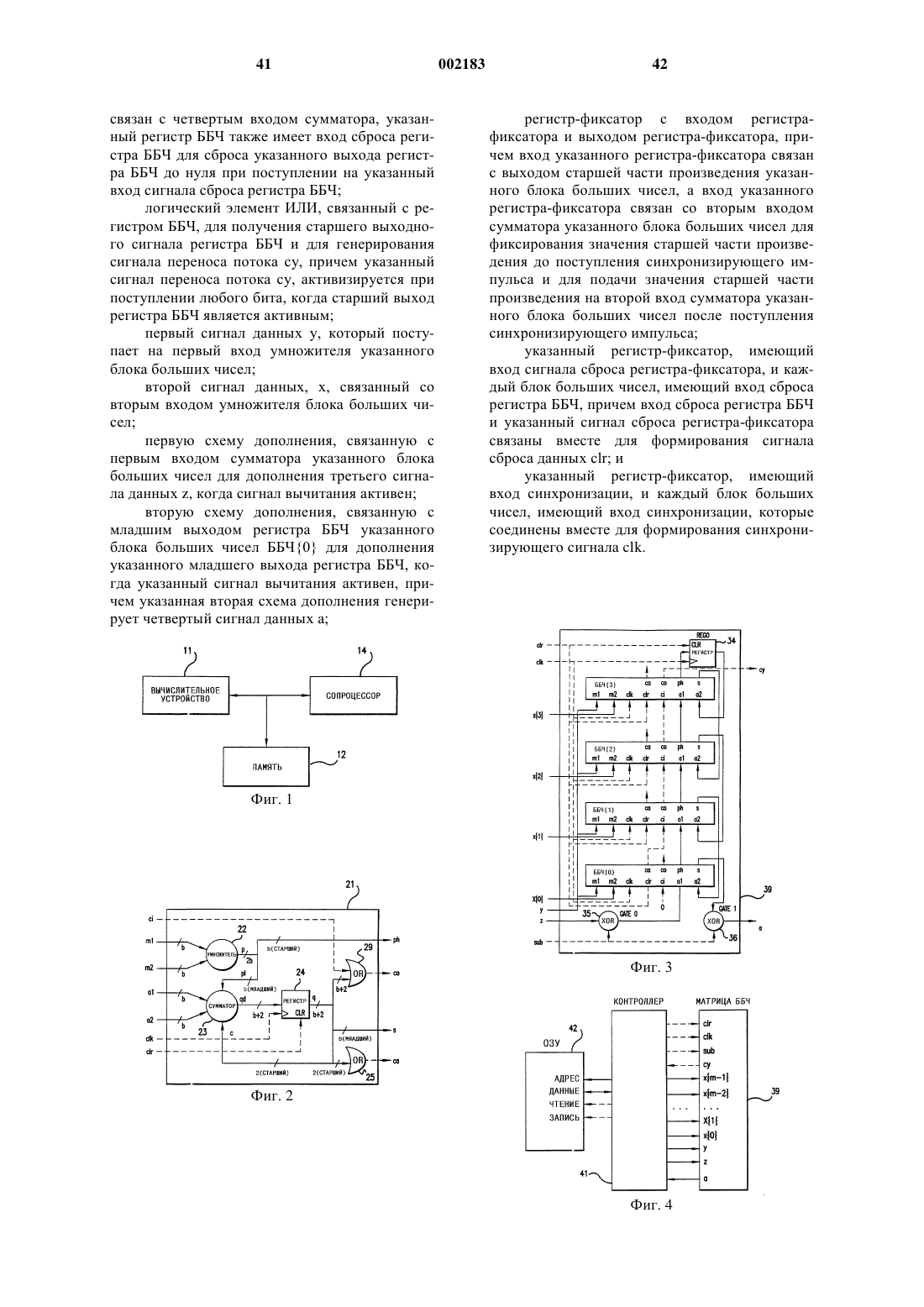

1. Арифметическое устройство для работы с целыми числами с многократно увеличенной точностью для обработки первого сигнала данных y со вторым сигналом данных х, включающее

множество блоков больших чисел (ББЧ), ББЧ{0}, ББЧ{1}, ББЧ{2},..., ББЧ{n-1}, где n - общее количество блоков больших чисел во множестве блоков больших чисел, причем каждый блок больших чисел содержит

умножитель с первым входом умножителя, вторым входом умножителя, выходом старшей части произведения и выходом младшей части произведения;

сумматор с первым входом сумматора, вторым входом сумматора, третьим входом сумматора, четвертым входом сумматора и выходом сумматора, причем указанный третий вход сумматора соединен с умножителем для приема выхода младшей части произведения; и

регистр ББЧ со входом регистра ББЧ и выходом регистра ББЧ, причем указанный вход регистра ББЧ связан с сумматором для приема выхода сумматора, указанный регистр ББЧ, фиксирующий значение выхода сумматора до получения синхронизирующего импульса и передающий значение на указанный выход регистра ББЧ после получения синхронизирующего импульса, указанный выход регистра ББЧ разделяют на старший выход регистра ББЧ и младший выход регистра ББЧ, указанный старший выход регистра ББЧ содержит два верхних бита указанного выхода регистра ББЧ, указанный младший выход регистра ББЧ содержит все биты указанного выхода регистра ББЧ, кроме тех, которые находятся в указанном старшем выходе регистра ББЧ, указанный старший выход регистра ББЧ связан с четвертым входом сумматора, указанный регистр ББЧ также имеет вход сброса регистра ББЧ для сброса указанного выхода регистра ББЧ до нуля при активизировании указанного входа сброса регистра ББЧ;

первый логический элемент ИЛИ, связанный с регистром ББЧ для приема выходного сигнала регистра ББЧ и входного сигнала переноса ci и для генерирования выходного сигнала переноса со, причем указанный выходной сигнал переноса со активизируется любым одним битом либо с выхода регистра ББЧ, который является активным, либо из входного сигнала переноса ci, который является активным;

второй логический элемент ИЛИ, связанный с регистром ББЧ для приема выходного старшего сигнала регистра ББЧ и для генерирования вспомогательного выходного сигнала переноса са, причем указанный вспомогательный выходной сигнал переноса са активизируется, если активен любой бит выходного старшего сигнала регистра ББЧ; причем

на первый вход умножителя каждого блока больших чисел указанного множества блоков больших чисел поступает первый сигнал данных у,

на вторые входы умножителей каждого блока больших чисел указанного множества блоков больших чисел (ББЧ), ББЧ{0}, ББЧ{1}, ББЧ{2},..., ББЧ{n-1} поступает соответственно каждый элемент из множества элементов х{0}, х{1}, х{2},..., х{n-1} второго сигнала данных х;

первый вход сумматора каждого i-го блока больших чисел ББЧ{i} указанного множества блоков больших чисел для i больше нуля связан с выходом старшей части произведения {i-1}-го блока больших чисел ББЧ{i-1};

младший выход регистра ББЧ каждого i-го блока больших чисел ББЧ{i} для i больше нуля связан со вторым входом сумматора {i-1}-го блока больших чисел ББЧ{i-1};

первую схему дополнения, связанную с первым входом сумматора первого блока больших чисел ББЧ{0} для дополнения третьего сигнала данных z, когда сигнал вычитания активен;

вторую схему дополнения, связанную с младшим выходом регистра ББЧ первого блока больших чисел ББЧ{0} для дополнения указанного младшего выхода регистра ББЧ, когда указанный сигнал вычитания активен, причем указанная вторая схема дополнения генерирует четвертый сигнал данных а;

регистр-фиксатор с входом регистра-фиксатора и выходом регистра-фиксатора, причем вход указанного регистра-фиксатора связан с выходом старшей части произведения указанного n-го блока больших чисел ББЧ{n-1}, а вход указанного регистра-фиксатора связан со вторым входом сумматора указанного n-го блока больших чисел ББЧ{n-1} для фиксирования значения n-ной старшей части произведения до поступления синхронизирующего импульса и для подачи значения n-ной старшей части произведения ко второму входу сумматора указанного n-го блока больших чисел после поступления синхронизирующего импульса;

указанный первый блок больших чисел ББЧ{0}, вход ci которого связан с логическим значением 0;

указанный второй блок больших чисел ББЧ{1}, вход ci которого связан с выходом са первого блока больших чисел ББЧ{0};

каждый i-тый блок больших чисел ББЧ{i} указанного множества блоков больших чисел для i более чем один, у которого вход ci связан с выводом со {i-1}-го блока больших чисел ББЧ{i-1}, а выход со n-го блока больших чисел ББЧ{n-1} является пятым сигналом данных, сигналом переноса потока су;

указанный регистр-фиксатор имеет вход для сигнала сброса регистра-фиксатора и каждый ББЧ имеет вход сброса регистра ББЧ, причем множество входов сброса регистра ББЧ и указанный вход сигнала сброса регистра-фиксатора связаны вместе для формирования сигнала сброса данных сlr; и

указанный регистр-фиксатор имеет вход синхронизации и каждый ББЧ имеет вход синхронизации, причем множество входов синхронизации соединены вместе для формирования синхронизирующего сигнала clk.

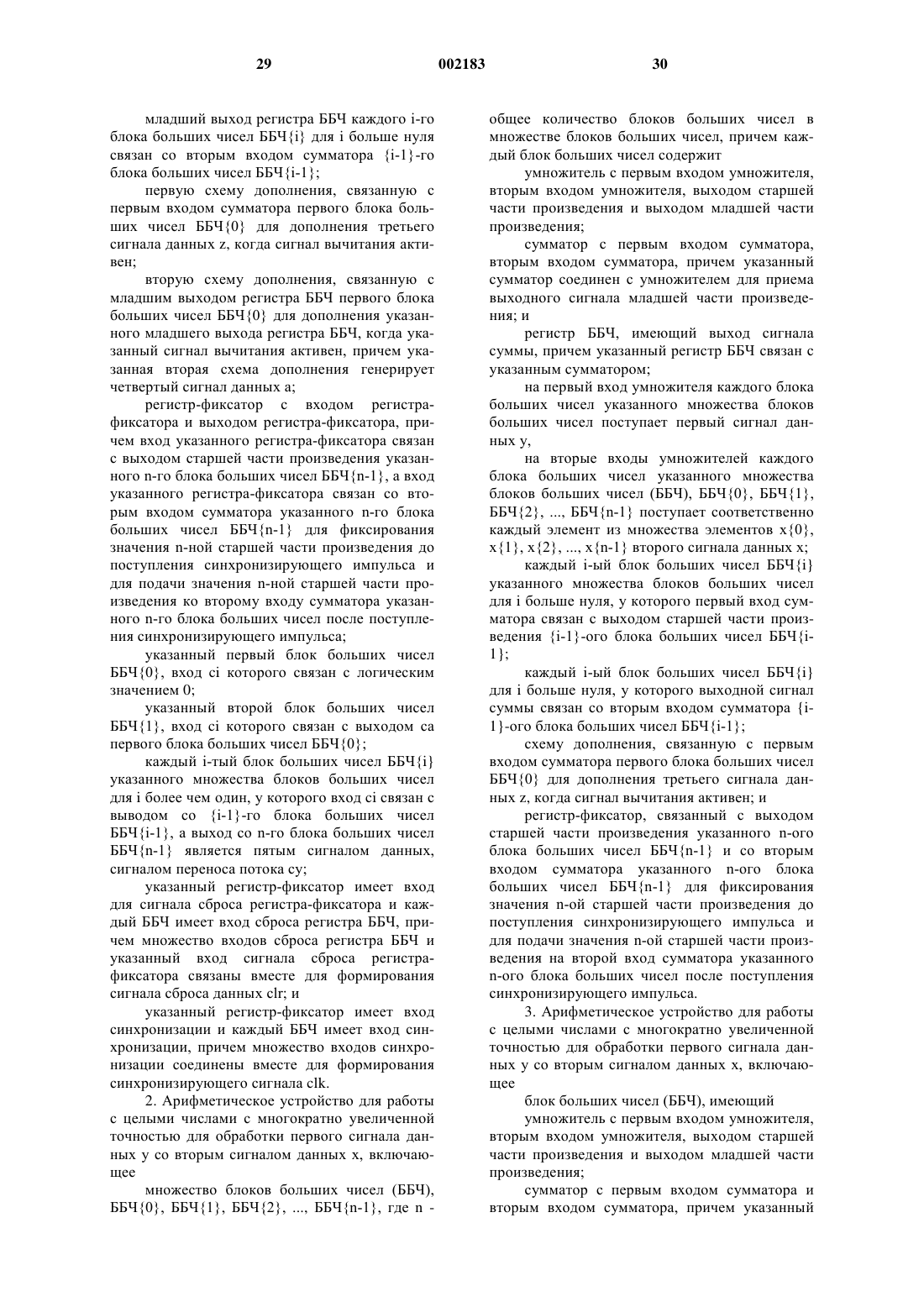

2. Арифметическое устройство для работы с целыми числами с многократно увеличенной точностью для обработки первого сигнала данных у со вторым сигналом данных х, включающее

множество блоков больших чисел (ББЧ), ББЧ{0}, ББЧ{1}, ББЧ{2},..., ББЧ{n-1}, где n - общее количество блоков больших чисел в множестве блоков больших чисел, причем каждый блок больших чисел содержит

умножитель с первым входом умножителя, вторым входом умножителя, выходом старшей части произведения и выходом младшей части произведения;

сумматор с первым входом сумматора, вторым входом сумматора, причем указанный сумматор соединен с умножителем для приема выходного сигнала младшей части произведения; и

регистр ББЧ, имеющий выход сигнала суммы, причем указанный регистр ББЧ связан с указанным сумматором;

на первый вход умножителя каждого блока больших чисел указанного множества блоков больших чисел поступает первый сигнал данных у,

на вторые входы умножителей каждого блока больших чисел указанного множества блоков больших чисел (ББЧ), ББЧ{0}, ББЧ{1}, ББЧ{2},..., ББЧ{n-1} поступает соответственно каждый элемент из множества элементов х{0}, х{1}, х{2},..., х{n-1} второго сигнала данных х;

каждый i-ый блок больших чисел ББЧ{i} указанного множества блоков больших чисел для i больше нуля, у которого первый вход сумматора связан с выходом старшей части произведения {i-1}-ого блока больших чисел ББЧ{i-1};

каждый i-ый блок больших чисел ББЧ{i} для i больше нуля, у которого выходной сигнал суммы связан со вторым входом сумматора {i-1}-ого блока больших чисел ББЧ{i-1};

схему дополнения, связанную с первым входом сумматора первого блока больших чисел ББЧ{0} для дополнения третьего сигнала данных z, когда сигнал вычитания активен; и

регистр-фиксатор, связанный с выходом старшей части произведения указанного n-ого блока больших чисел ББЧ{n-1} и со вторым входом сумматора указанного n-ого блока больших чисел ББЧ{n-1} для фиксирования значения n-ой старшей части произведения до поступления синхронизирующего импульса и для подачи значения n-ой старшей части произведения на второй вход сумматора указанного n-ого блока больших чисел после поступления синхронизирующего импульса.

3. Арифметическое устройство для работы с целыми числами с многократно увеличенной точностью для обработки первого сигнала данных у со вторым сигналом данных х, включающее

блок больших чисел (ББЧ), имеющий

умножитель с первым входом умножителя, вторым входом умножителя, выходом старшей части произведения и выходом младшей части произведения;

сумматор с первым входом сумматора и вторым входом сумматора, причем указанный сумматор связан с умножителем для приема выходного сигнала младшей части произведения и для вывода первого сигнала суммы; и

регистр ББЧ, связанный с указанным сумматором для приема первого сигнала суммы и для вывюфр второго сигнала суммы, причем

на первый вход умножителя указанного блока больших чисел поступает первый сигнал данных у;

на второй вход умножителя указанного блока больших чисел поступает второй сигнал данных х;

схему дополнения, связанную с первым входом сумматора указанного блока больших чисел для дополнения третьего сигнала данных z, когда сигнал вычитания активен; и

регистр-фиксатор, связанный с выходом старшей части произведения указанного блока больших чисел и со вторым входом сумматора указанного блока больших чисел для фиксации значения старшей части произведения до поступления синхронизирующего импульса и для подачи значения старшей части произведения к второму входу сумматора указанного блока больших чисел после поступления синхронизирующего импульса.

4. Устройство по п.3, в котором указанный блок больших чисел дополнительно включает логический элемент ИЛИ, соединенный с выходом указанного регистра ББЧ, для приема верхних битов второго сигнала суммы из указанного регистра ББЧ в качестве сигнала переноса, причем указанный второй логический элемент ИЛИ выводит логическое ИЛИ сигнала переноса в качестве сигнала переноса потока.

5. Устройство по п.3 или 4, дополнительно включающее

множество блоков больших чисел, ББЧ{0}, ББЧ{1}, ББЧ{2},..., ББЧ{n-1}, где n - общее количество блоков больших чисел во множестве блоков больших чисел;

каждый i-ый блок больших чисел ББЧ{i} указанного множества блоков больших чисел для i больше нуля, у которого первый вход сумматора связан с выходом старшей части произведения {i-1}-ого блока больших чисел ББЧ{i-1}; и

каждый i-ый блок больших чисел ББЧ{i} для i больше нуля, у которого выход сигнала суммы связан со вторым входом сумматора {i-1}-ого блока больших чисел ББЧ{i-1}.

6. Арифметическое устройство для работы с целыми числами с многократно увеличенной точностью для обработки первого сигнала данных х со вторым сигналом данных у, включающее

множество блоков больших чисел (ББЧ), в котором каждый блок больших чисел имеет

умножитель с первым входом умножителя, вторым входом умножителя, выходом старшей части произведения, выходом младшей части произведения;

сумматор с первым входом сумматора и вторым входом сумматора, причем сумматор соединен с умножителем для приема выходного сигнала младшей части произведения и вывода сигнала суммы;

регистр ББЧ, соединенный с указанным сумматором для приема первого сигнала суммы и для вывода второго сигнала суммы;

на первый вход умножителя каждого блока больших чисел указанного множества блоков больших чисел подается первый сигнал данных у;

с каждым вторым входом умножителя каждого блока больших чисел указанного множества блоков больших чисел соответственно связан каждый элемент второго сигнала данных х, имеющего множество элементов;

каждый i-ый блок больших чисел ББЧ{i} указанного множества блоков больших чисел для i, отличного от исходного блока больших чисел, имеет первый вход сумматора, связанный с выходом старшей части произведения {i-1}-ого блока больших чисел ББЧ{i-1};

каждый i-ый блок больших чисел ББЧ{i} для i, отличного от исходного блока больших чисел, имеет выход сигнала суммы, связанный со вторым входом сумматора {i-1}-ого блока больших чисел ББЧ{i-1}.

7. Арифметическое устройство для работы с целыми числами с многократно увеличенной точностью по п.6, дополнительно включающее

схему дополнения, связанную с первым входом сумматора первого блока больших чисел ББЧ{0} для дополнения третьего сигнала данных z, когда сигнал вычитания активен; и

регистр-фиксатор, связанный с выходом старшей части произведения n-ого блока больших чисел ББЧ{n-1} и со вторым входом сумматора указанного n-ого блока больших чисел ББЧ{n-1}, где n - общее количество блоков больших чисел, для фиксирования значения n-ого выхода старшей части произведения до поступления синхронизирующего импульса и для подачи значения n-ого выхода старшей части произведения на второй вход сумматора указанного n-ого блока больших чисел после поступления синхронизирующего импульса.

8. Арифметическое устройство для работы с целыми числами с многократно увеличенной точностью по п.6, дополнительно включающее схему дополнения, связанную с первым входом сумматора первого блока больших чисел ББЧ{0}, для дополнения третьего сигнала данных z, когда сигнал вычитания активен.

9. Арифметическое устройство для работы с целыми числами с многократно увеличенной точностью по п.6 или 8, дополнительно включающее регистр-фиксатор, связанный с выходом старшей части произведения n-ого блока больших чисел ББЧ{n-1} и со вторым входом сумматора указанного n-ого блока больших чисел ББЧ{n-1}, где n - общее количество блоков больших чисел во множестве блоков больших чисел, для фиксирования значения n-ого выхода старшей части произведения до поступления синхронизирующего импульса и для подачи значения n-ого выхода старшей части произведения на второй вход сумматора указанного n-ого блока больших чисел после поступления синхронизирующего импульса.

10. Арифметическое устройство для работы с целыми числами с многократно увеличенной точностью по п.6, дополнительно включающее

логическое средство, связанное с первым входом сумматора первого блока больших чисел ББЧ{0} для дополнения третьего сигнала данных z, когда сигнал вычитания активен; и

средство регистра, связанное с выходом старшей части произведения n-ого блока больших чисел ББЧ{n-1} и со вторым входом сумматора указанного n-ого блока больших чисел ББЧ{n-1}, где n - общее количество блоков больших чисел во множестве блоков больших чисел, для фиксирования значения n-ого выхода старшей части произведения до поступления синхронизирующего импульса и для подачи значения n-ого выхода старшей части произведения на второй вход сумматора указанного n-ого блока больших чисел после поступления синхронизирующего импульса.

11. Арифметическое устройство для работы с целыми числами с многократно увеличенной точностью по п.6, далее включающее логическое средство, связанное с первым входом сумматора первого блока больших чисел ББЧ{0} для дополнения третьего сигнала данных z, когда сигнал вычитания активен.

12. Арифметическое устройство для работы с целыми числами с многократно увеличенной точностью по п.6 или 11, дополнительно включающее средство регистра, связанное с выходом старшей части произведения n-ого блока больших чисел ББЧ{n-1} и со вторым входом сумматора указанного n-ого блока больших чисел ББЧ{n-1}, где n - общее количество блоков больших чисел во множестве блоков больших чисел для фиксирования значения n-ого выхода старшей части произведения до поступления синхронизирующего импульса и для подачи значения n-ого выхода старшей части произведения на второй вход сумматора указанного n-ого блока больших чисел после поступления синхронизирующего импульса.

13. Арифметическое устройство для работы с целыми числами с многократно увеличенной точностью по п.2, дополнительно включающее выходную схему, связанную с выходом сигнала суммы первого блока больших чисел ББЧ{0} для вывода выходного сигнала.

14. Арифметическое устройство для работы с целыми числами с многократно увеличенной точностью по п.3, дополнительно включающее выходную схему, связанную с выходом сигнала суммы указанного блока больших чисел для вывода выходного сигнала.

15. Арифметическое устройство для работы с целыми числами с многократно увеличенной точностью для обработки первого сигнала данных х со вторым сигналом данных у, включающее

блок больших чисел (ББЧ), имеющий

умножитель с первым входом умножителя, вторым входом умножителя, выходом старшей части произведения и выходом младшей части произведения;

сумматор с первым входом сумматора и вторым входом сумматора, причем указанный сумматор связан с умножителем для приема выходного сигнала младшей части произведения и предназначен для вывода первого сигнала суммы; и

регистр ББЧ, связанный с указанным сумматором для приема первого сигнала суммы и для вывода второго сигнала суммы;

логический элемент ИЛИ, соединенный с выходом указаннюую регистра ББЧ для приема верхних битов второго сигнала суммы из указанного регистра ББЧ в качестве сигнала переноса, а также для вывода логического ИЛИ сигнала переноса в качестве сигнала переноса потока;

на первый вход умножителя указанного блока больших чисел подается первый сигнал данных у;

ко второму входу умножителя указанного блока больших чисел подается второй сигнал данных х.

16. Арифметическое устройство для работы с целыми числами с многократно увеличенной точностью по п.15, дополнительно включающее

схему дополнения, связанную с первым входом сумматора указанного блока больших чисел для дополнения третьего сигнала данных z, когда сигнал вычитания активен; и

регистр-фиксатор, связанный с выходом старшей части произведения указанного блока больших чисел и вторым входом сумматора указанного блока больших чисел для фиксирования значения выхода старшей части произведения до поступления синхронизирующего импульса и для подачи значения выхода старшей части произведения на второй вход сумматора указанного блока больших чисел после поступления синхронизирующего импульса.

17. Арифметическое устройство для работы с целыми числами с многократно увеличенной точностью по п.15, дополнительно включающее схему дополнения, связанную с первым входом сумматора указанного блока больших чисел для дополнения третьего сигнала данных z, когда сигнал вычитания активен.

18. Арифметическое устройство для работы с целыми числами с многократно увеличенной точностью по п.15 или 17, далее включающее регистр-фиксатор, связанный с выходом старшей части произведения указанного блока больших чисел и со вторым входом сумматора указанного блока больших чисел, для фиксирования значения выхода старшей части произведения до поступления синхронизирующего импульса и для подачи значения выхода старшей части произведения на второй вход сумматора указанного блока больших чисел после поступления синхронизирующего импульса.

19. Способ обработки первого сигнала данных у со вторым сигналом данных х, использующий матрицу блоков больших чисел (ББЧ), имеющую, по крайней мере, один блок больших чисел, причем каждый блок больших чисел имеет умножитель, сумматор и регистр ББЧ, умножитель имеет первый вход умножителя, второй вход умножителя, выход старшей части произведения, выход младшей части произведения, сумматор имеет первый вход сумматора и второй вход сумматора, а указанный сумматор соединен с умножителем для приема выхода младшей части произведения и вывода первого сигнала суммы, а также регистр ББЧ, соединенный с указанным сумматором для приема первого сигнала суммы и для вывода второго сигнала суммы, причем матрица больших чисел имеет вход сброса, вход вычитания, вход синхронизации, вход данных z и выход данных а,

указанный метод включает следующие шаги:

подачу импульса на вход сброса для сброса регистра ББЧ и регистра-фиксатора в пределах матрицы ББЧ;

установку входа вычитания на одну из логических единиц для вычитания и на логический ноль для сложения;

подачу значения для второго сигнала данных х в массив ББЧ;

подачу значения для первого сигнала данных у в массив ББЧ;

подачу значения для ввода данных z в массив ББЧ;

подачу импульса на вход синхронизации для обновления множества регистров ББЧ и регистра-фиксатора новыми значениями;

считывание выхода данных а.

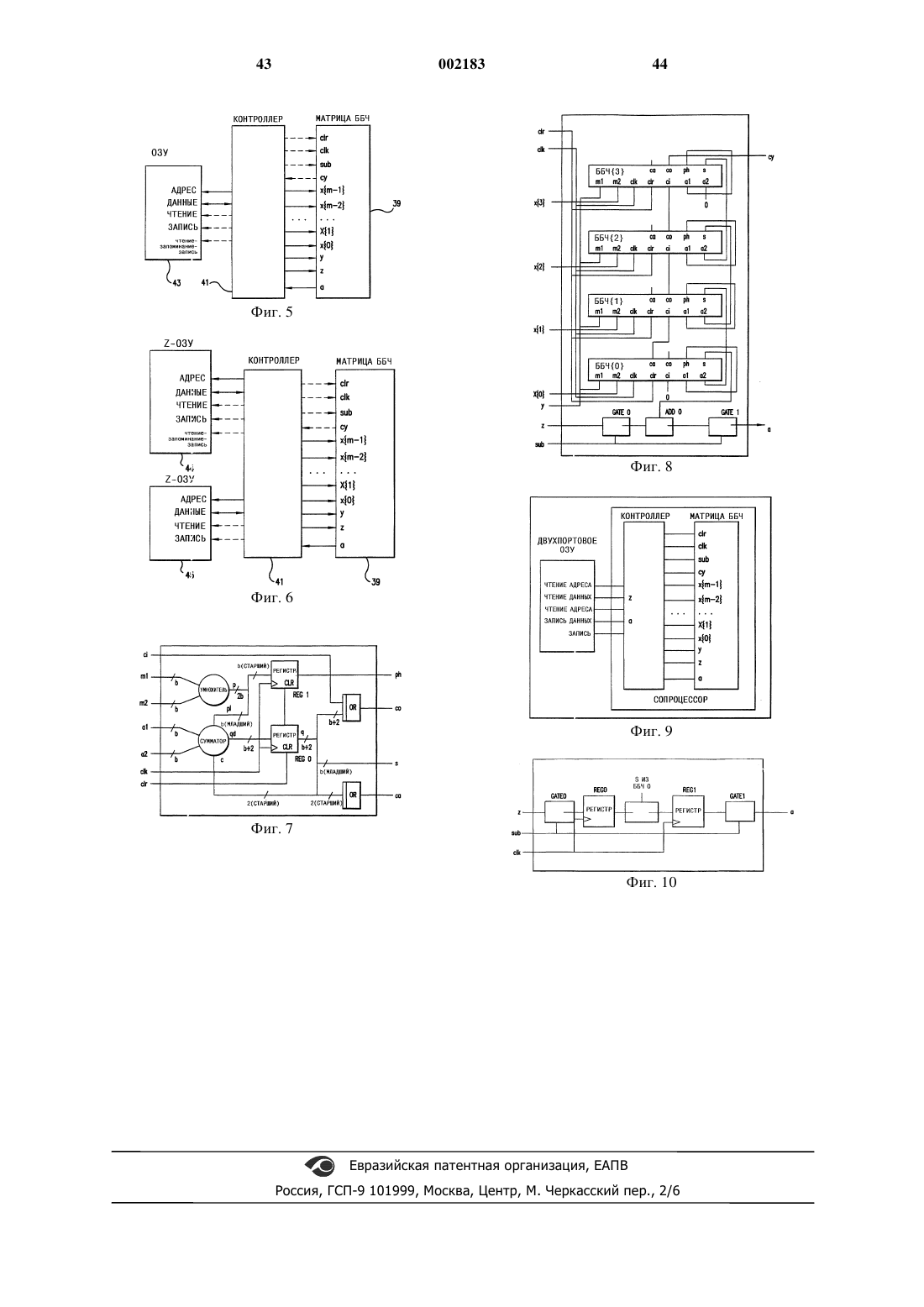

20. Арифметическое устройство для работы с целыми числами с многократно увеличенной точностью, включающее

матрицу блоков больших чисел (ББЧ) из множества блоков больших чисел, которая имеет вход сброса, вход вычитания, множество входов данных х{0}, х{1}, ..., х{m-1}, вход у, вход z, вход синхронизации и выход а;

причем каждый блок больших чисел указанной матрицы (ББЧ) имеет умножитель с первым входом умножителя, вторым входом умножителя, выходом старшей части произведения и выходом младшей части произведения;

сумматор с первым входом сумматора и вторым входом сумматора, причем указанный сумматор связан с умножителем для приема выходного сигнала младшей части произведения и для вывода первого сигнала суммы; и

регистр ББЧ, связанный с указанным сумматором для приема первого сигнала суммы и для вывода второго сигнала суммы;

контроллер, соединенный с указанным блоком больших чисел (ББЧ) для подачи импульса на вход сброса, для выбора значения активизации и дезактивизации на входе вычитания, для считывания и подачи m значений на множество входов данных х{0}, х{1},..., х{m-1} соответственно для считывания и подачи значения у на вход у, для считывания и подачи значения z на вход z, подачи импульса на вход синхронизации, считывания значения с выхода а и для записи значения выхода а в оперативную память; и

оперативное запоминающее устройство (ОЗУ), соединенное с указанным контроллером для хранения m значений, считываемых контроллером, для хранения значения у, считываемого контроллером, для хранения значения z, считываемого контроллером, и для хранения значения выхода а, записанного контроллером.

21. Арифметическое устройство для работы с целыми числами с многократно увеличенной точностью, включающее

матрицу блока больших чисел (ББЧ) множества блоков больших чисел, имеющую вход сброса, вход вычитания, вход данных х, вход у, вход z, вход синхронизации и выход а;

причем каждый блок больших чисел имеет

умножитель с первым входом умножителя, вторым входом умножителя, выходом старшей части произведения и выходом младшей части произведения;

сумматор с первым входом сумматора и вторым входом сумматора, причем указанный сумматор связан с умножителем для приема выходного сигнала младшей части произведения и для вывода первого сигнала суммы; и

регистр ББЧ, связанный с указанным сумматором для приема первого сигнала суммы и для вывода второго сигнала суммы;

контроллер, соединенный с указанным блоком больших чисел (ББЧ) для подачи импульса на вход сброса, для выбора значения активизации и дезактивизации на входе вычитания, для считывания и подачи m значений на вход данных х, для считывания и подачи значения у на вход у, для считывания и подачи значения z на вход z, подачи импульса на вход синхронизации, считывания значения с выхода а и для записи значения выхода а в оперативное запоминающее устройство; и

оперативное запоминающее устройство (ОЗУ), соединенное с указанным контроллером для хранения m значений, считываемых контроллером, хранения значения у, считываемого контроллером, хранения значения z, считываемого контроллером, и хранения значения выхода а, записанного контроллером.

22. Арифметическое устройство для работы с целыми числами с многократно увеличенной точностью по п.20 или 21, в котором оперативное запоминающее устройство способно выполнять операцию "чтение-преобразование-запись" таким образом, что по сигналу контроллера значение а считывается из оперативного запоминающего устройства, преобразовывается и записывается назад в оперативное запоминающее устройство за один цикл.

23. Арифметическое устройство для работы с целыми числами с многократно увеличенной точностью по п.20 или 21, в котором оперативное запоминающее устройство дополнительно включает

первое оперативное запоминающее устройство для хранения значения z, которое способно выполнять операцию "чтение-преобразование-запись", второе оперативное запоминающее устройство для хранения значения у, в котором контроллер одновременно считывает значение у и выполняет операцию "чтение-преобразование- запись" со значением z за один цикл оперативного запоминающего устройства.

24. Арифметическое устройство для работы с целыми числами с многократно увеличенной точностью по п.20 или 21, у которого оперативное запоминающее устройство имеет один порт записи и один порт чтения, так что по сигналу контроллера первое значение считывается с первого адреса, в то время как одновременно второе значение записывается во второй адрес.

25. Арифметическое устройство для работы с целыми числами с многократно увеличенной точностью для обработки первого сигнала данных у со вторым сигналом данных х, включающее:

множество блоков больших чисел (ББЧ), ББЧ{0}, ББЧ{1}, ББЧ{2},..., ББЧ{n-1}, где "n" - общее количество блоков больших чисел во множестве блоков больших чисел, причем каждый блок больших чисел имеет

умножитель с первым входом умножителя, вторым входом умножителя, выходом старшей части произведения и выходом младшей части произведения;

сумматор с первым входом сумматора и вторым входом сумматора, третьим входом сумматора, четвертым входом сумматора и входом сумматора причем указанный третий вход сумматора соединен с умножителем для приема выходного сигнала младшей части произведения; и

первый регистр ББЧ со входом регистра ББЧ и выходом регистра ББЧ, причем указанный вход регистра ББЧ связан с сумматором для приема выхода сумматора, указанный первый регистр ББЧ фиксирует значение выхода сумматора до поступления синхронизирующего импульса и передает значение на указанный выход регистра ББЧ после поступления синхронизирующего импульса, причем выходной сигнал указанного регистра ББЧ разделяется на старший выходной сигнал регистра ББЧ и младший выходной сигнал регистра ББЧ, причем указанный старший выходной сигнал регистра ББЧ, содержит два верхних бита указанного выходного сигнала регистра ББЧ, а указанный младший выходной сигнал регистра ББЧ содержит все биты указанного выходного сигнала регистра ББЧ, кроме тех, которые находятся в указанном выходном сигнале регистра ББЧ, указанный выходной сигнал регистра ББЧ связан с четвертым входом сумматора, причем указанный первый регистр ББЧ также имеет вход сброса регистра ББЧ для сброса указанного выхода регистра ББЧ до нуля, когда активизируется указанный вход сброса регистра ББЧ;

второй регистр ББЧ для приема выхода старшей части произведения умножителя;

первый логический элемент ИЛИ, связанный с первым регистром ББЧ для получения выхода регистра ББЧ и входного сигнала переноса сi и для генерирования выходного несущего сигнала со, который активизируется в ответ на один сигнал любого бита с выхода регистра ББЧ, являющегося активным, и указанного сигнала ci, являющегося активным;

второй логический элемент ИЛИ, связанный с первым регистром ББЧ для приема выходного старшего сигнала регистра ББЧ и для генерирования вспомогательного входного сигнала переноса са, причем указанный вспомогательный входной сигнал переноса са активизируется, если активен любой бит выходного старшего сигнала регистра ББЧ;

первый сигнал данных у, который поступает на первый вход умножителя каждого блока больших чисел указанного множества блоков больших чисел;

второй сигнал данных х, имеющий множество элементов х{0}, х{1}, х{2},..., х{n-1}, причем каждый элемент соответственно связан со вторым входом умножителя каждого блока больших чисел указанного множества блоков больших чисел;

каждый i-тый блок больших чисел ББЧ{i} указанного множества блоков больших чисел, у которого первый вход сумматора связан с выходом старшей части произведения соответствующего i-ого блока больших чисел ББЧ{i};

каждый i-тый блок больших чисел ББЧ{i} для i больше нуля имеет младший выход регистра ББЧ, связанный со вторым входом сумматора {i-1}-го блока больших чисел ББЧ{i-1};

первую схему дополнения, связанную с первым входом сумматора первого блока больших чисел ББЧ{0} для дополнения третьего сигнала данных z, когда сигнал вычитания активен;

вторую схему дополнения, связанную с младшим выходом регистра ББЧ первого блока больших чисел ББЧ{0} для дополнения указанного младшего выхода регистра ББЧ, когда указанный сигнал вычитания активен, причем указанная вторая схема дополнения генерирует четвертый сигнал данных а;

указанный первый блок больших чисел ББЧ{0}, вход ci которого связан с логическим значением 0;

указанный второй блок больших чисел ББЧ{1}, вход ci которoго связан с выходом са первого блока больших чисел ББЧ{0};

каждый n-ый блок больших чисел ББЧ{n-1}, у которого второй вход сумматора связан с логическим значением 0;

каждый i-тый блок больших чисел ББЧ{i} указанного множества блоков больших чисел для i более единицы, у которого вход ci связан с выходом со {i-1}-го блока больших чисел ББЧ{i-1}, причем со выход n-го блока больших чисел ББЧ{n-1} является пятым сигналом данных - сигналом переноса потока су.

26. Арифметическое устройство для работы с целыми числами с многократно увеличенной точностью для обработки первого сигнала данных у со вторым сигналом данных х, включающее

блок больших чисел (ББЧ), имеющий

умножитель с первым входом умножителя, вторым входом умножителя, выходом старшей части произведения и выходом младшей части произведения;

сумматор с первым входом сумматора и вторым входом сумматора, третьим входом сумматора, четвертым входом сумматора и входом сумматора причем указанный третий вход сумматора соединен с умножителем для приема выходного сигнала младшей части произведения; и

первый регистр ББЧ со входом регистра ББЧ и выходом регистра ББЧ, причем указанный вход регистра ББЧ связан с сумматором для приема выхода сумматора, указанный первый регистр ББЧ фиксирует значение выхода сумматора до поступления синхронизирующего импульса и передает значение на указанный выход регистра ББЧ после поступления синхронизирующего импульса, причем выходной сигнал указанного регистра ББЧ разделяется на старший выходной сигнал регистра ББЧ и младший выходной сигнал регистра ББЧ, указанный старший выходной сигнал регистра ББЧ содержит два верхних бита указанного выходного сигнала регистра ББЧ, а указанный младший выходной сигнал регистра ББЧ содержит все биты указанного выходного сигнала регистра ББЧ, кроме тех, которые находятся в указанном выходном сигнале регистра ББЧ, указанный выходной старший сигнал регистра ББЧ связан с четвертым входом сумматора, причем указанный первый регистр ББЧ также имеет вход сброса регистра ББЧ для сброса указанного выхода регистра ББЧ до нуля, когда активизируется указанный вход сброса регистр ББЧ;

второй регистр ББЧ для приема выхода старшей части произведения умножителя;

первый логический элемент ИЛИ, связанный с первым регистром ББЧ для получения старшего выхода регистра ББЧ и для генерирования сигнала переноса потока су, который активизируется, когда сигнал любого бита с выхода регистра ББЧ является активным,

на первый вход умножителя указанного блока больших чисел поступает первый сигнал данных у;

на второй вход умножителя указанного блока больших чисел поступает второй сигнал данных х,

первую схему дополнения, связанную с первым входом сумматора указанного блока больших чисел для дополнения третьего сигнала данных z, когда сигнал вычитания активен;

вторую схему дополнения, связанную с младшим выходом регистра ББЧ указанного блока больших чисел, для дополнения указанного младшего выхода регистра ББЧ, когда указанный сигнал вычитания активен, указанная вторая схема дополнения генерирует четвертый сигнал данных а.

27. Арифметическое устройство для работы с целыми числами с многократно увеличенной точностью для обработки первого сигнала данных у со вторым сигналом данных х, включающее

блок больших чисел (ББЧ), имеющий

умножитель с первым входом умножителя, вторым входом умножителя, выходом старшей части произведения и выходом младшей части произведения;

сумматор с первым входом сумматора, вторым входом сумматора, третьим входом сумматора, четвертым входом сумматора и выходом сумматора, причем указанный третий вход сумматора соединен с умножителем для приема сигнала выхода младшей части произведения; и

регистр ББЧ со входом регистра ББЧ и выходом регистра ББЧ, указанный вход регистра ББЧ связан с сумматором для приема выхода сумматора, указанный регистр ББЧ фиксирует значение выхода сумматора до поступления синхронизирующего импульса и передает это значение на указанный выход регистра ББЧ после поступления синхронизирующего импульса, указанный выход регистра ББЧ разделяют на старший выход регистра ББЧ и младший выход регистра ББЧ, указанный старший выход регистра ББЧ содержит два верхних бита указанного выхода регистра ББЧ, указанный младший выход регистра ББЧ содержит все биты указанного выхода регистра ББЧ, кроме тех, котоЁых находятся в указанном старшем выходе регистра ББЧ, указанный старший выход регистра ББЧ связан с четвертым входом сумматора, указанный регистр ББЧ также имеет вход сброса регистра ББЧ для сброса указанного выхода регистра ББЧ до нуля при поступлении на указанный вход сигнала сброса регистра ББЧ;

логический элемент ИЛИ, связанный с регистром ББЧ, для получения старшего выходного сигнала регистра ББЧ и для генерирования сигнала переноса потока су, причем указанный сигнал переноса потока су, активизируется при поступлении любого бита, когда старший выход регистра ББЧ является активным;

первый сигнал данных у, который поступает на первый вход умножителя указанного блока больших чисел;

второй сигнал данных, х, связанный со вторым входом умножителя блока больших чисел;

первую схему дополнения, связанную с первым входом сумматора указанного блока больших чисел для дополнения третьего сигнала данных z, когда сигнал вычитания активен;

вторую схему дополнения, связанную с младшим выходом регистра ББЧ указанного блока больших чисел ББЧ{0} для дополнения указанного младшего выхода регистра ББЧ, когда указанный сигнал вычитания активен, причем указанная вторая схема дополнения генерирует четвертый сигнал данных а;

регистр-фиксатор с входом регистра-фиксатора и выходом регистра-фиксатора, причем вход указанного регистра-фиксатора связан с выходом старшей части произведения указанного блока больших чисел, а вход указанного регистра-фиксатора связан со вторым входом сумматора указанного блока больших чисел для фиксирования значения старшей части произведения до поступления синхронизирующего импульса и для подачи значения старшей части произведения на второй вход сумматора указанного блока больших чисел после поступления синхронизирующего импульса;

указанный регистр-фиксатор, имеющий вход сигнала сброса регистра-фиксатора, и каждый блок больших чисел, имеющий вход сброса регистра ББЧ, причем вход сброса регистра ББЧ и указанный сигнал сброса регистра-фиксатора связаны вместе для формирования сигнала сброса данных сlr; и

указанный регистр-фиксатор, имеющий вход синхронизации, и каждый блок больших чисел, имеющий вход синхронизации, которые соединены вместе для формирования синхронизирующего сигнала clk.

Текст