Устройство и способ обработки данных

Номер патента: 14413

Опубликовано: 30.12.2010

Авторы: Уилсон Джон Николас, Тейлор Мэтью Пол Атол, Атунгсири Сэмюель Асанбенг

Формула / Реферат

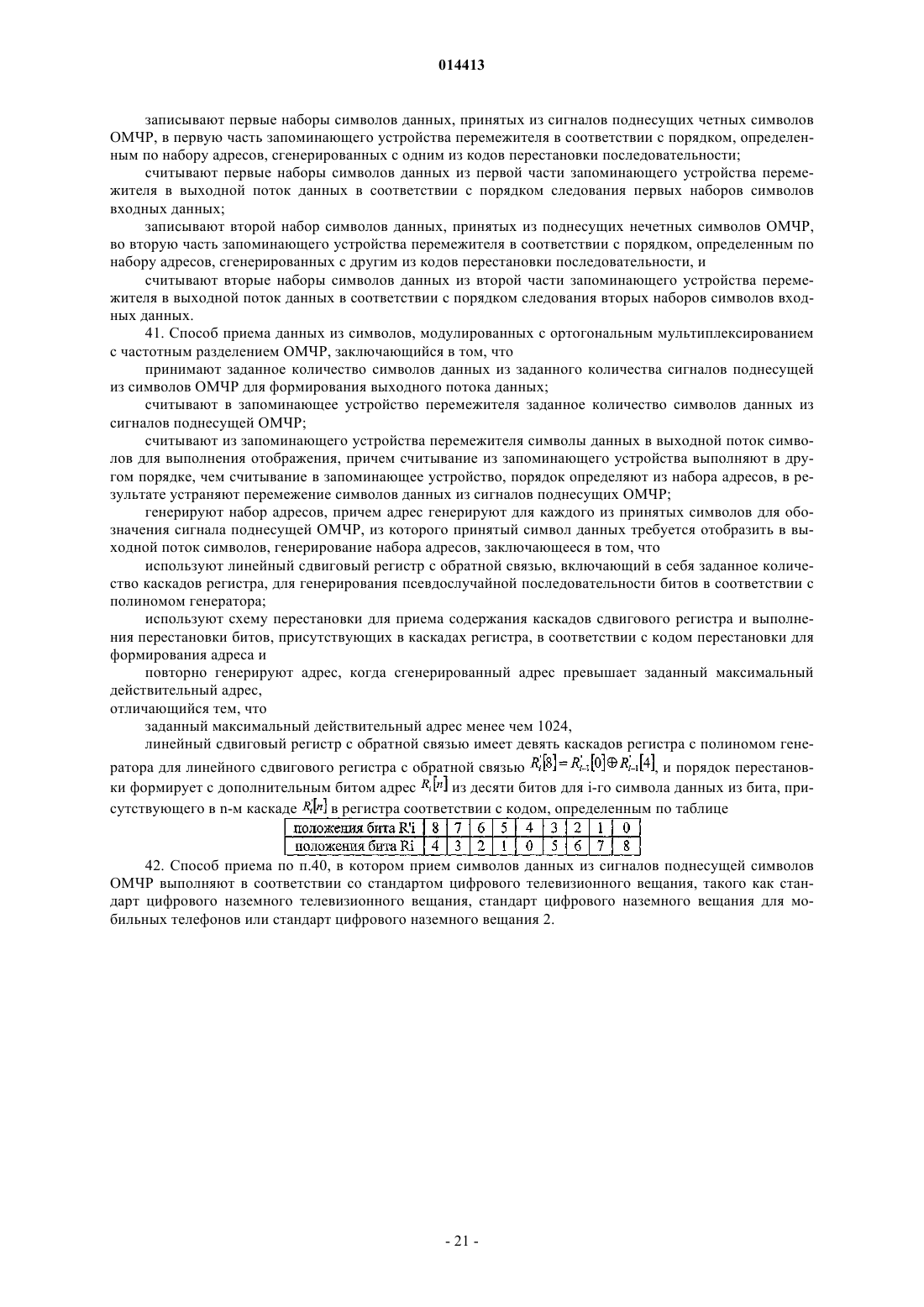

1. Устройство обработки данных, во время работы отображающее символы входных данных, предназначенных для передачи на заданное количество сигналов поднесущих ортогонально мультиплексированного с частотным разделением (ОМЧР) символа, содержащее

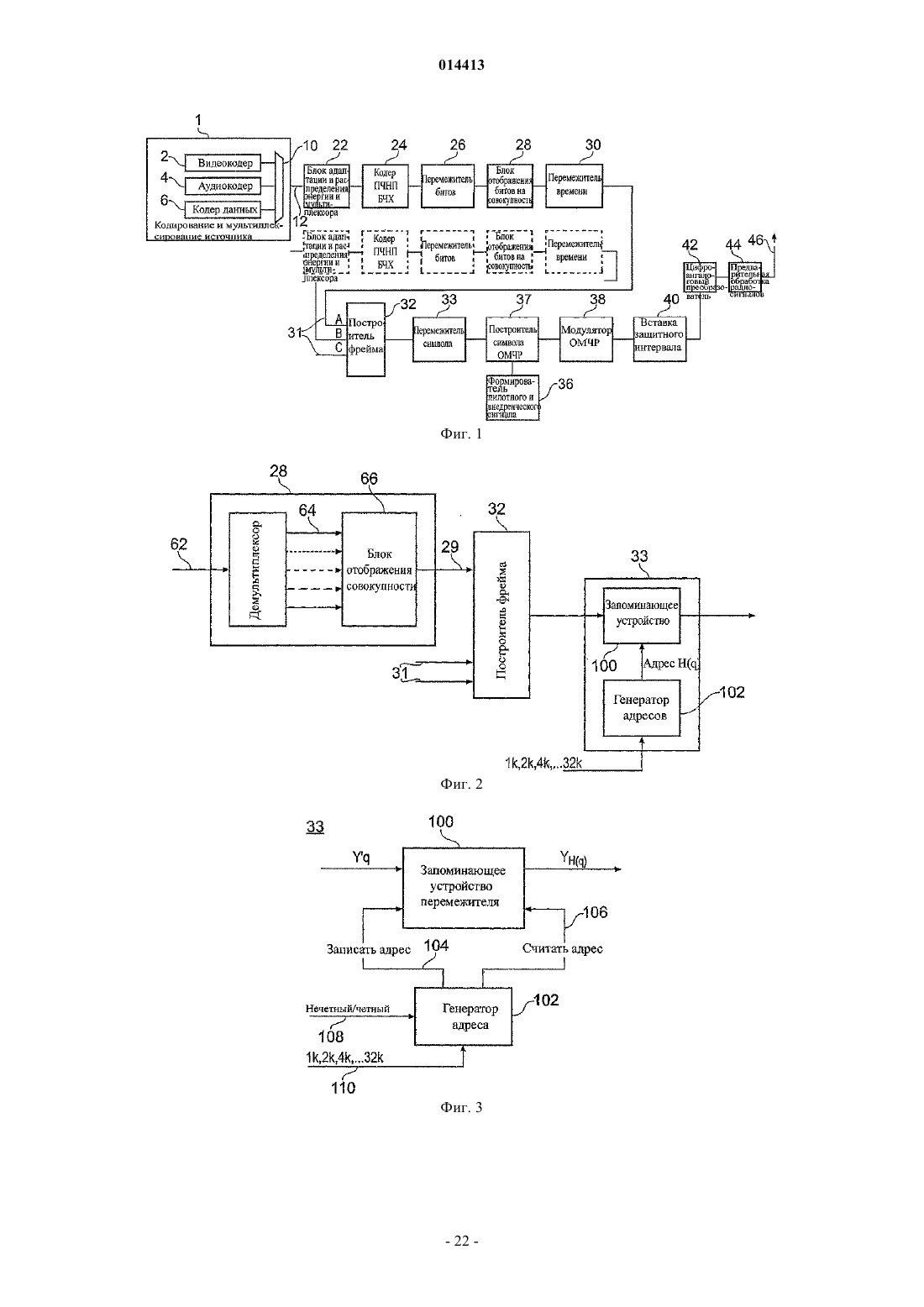

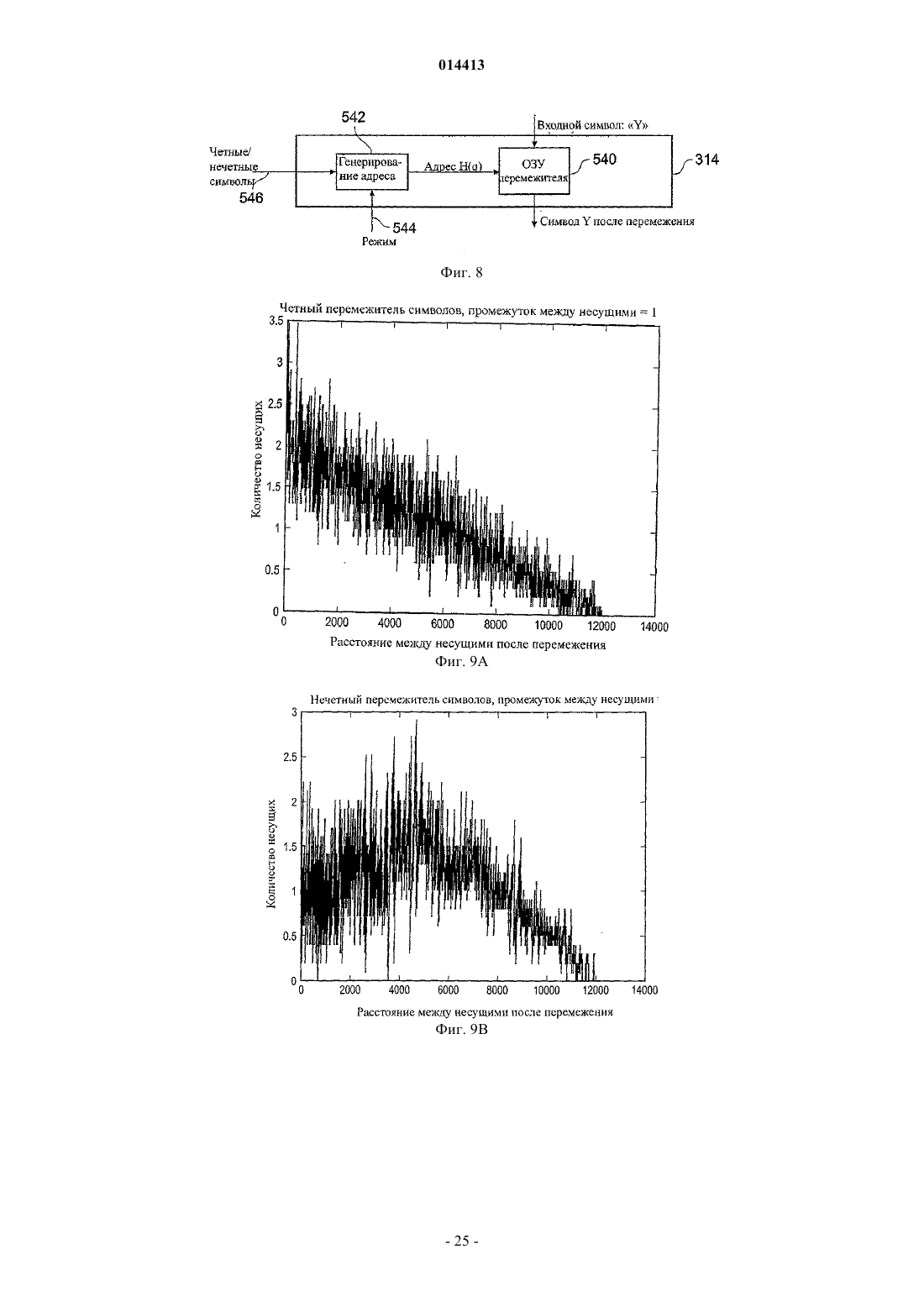

перемежитель, во время работы считывающий в запоминающее устройство перемежителя заданное количество символов входных данных для отображения на сигналы поднесущей ОМЧР и считывающий из запоминающего устройства перемежителя символы входных данных для поднесущих ОМЧР для выполнения отображения, причем считывание из запоминающего устройства выполняют в другом порядке, чем считывание в запоминающее устройство, порядок определяют по набору адресов, в результате чего выполняют перемежение символов данных на сигналы поднесущей;

генератор адреса, во время работы генерирующий набор адресов, причем адрес генерируют для каждого из символов входных данных, для обозначения одного из сигналов поднесущей, на который требуется отобразить символ данных, содержащий

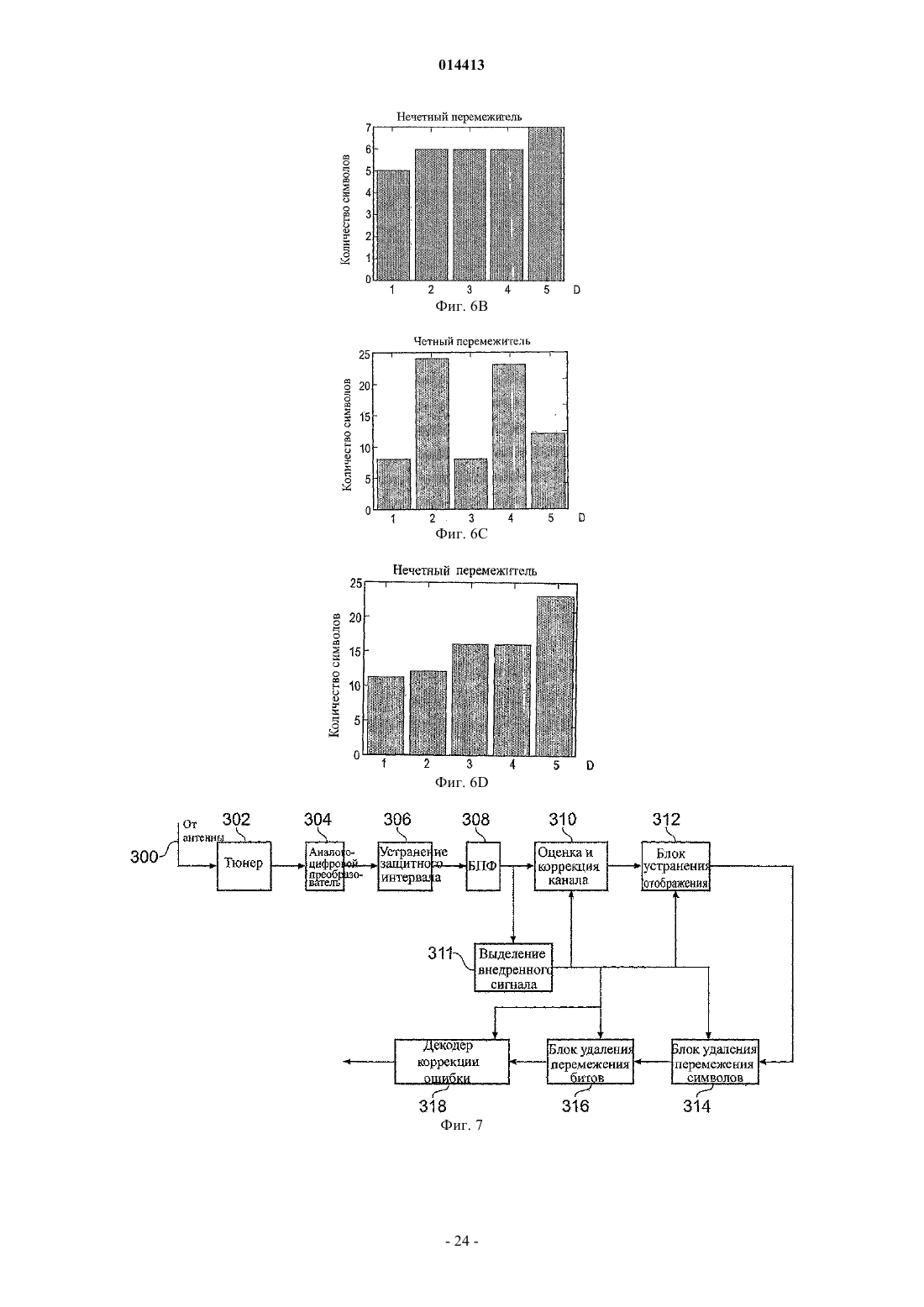

линейный сдвиговый регистр с обратной связью, включающий в себя заданное количество каскадов регистра и во время работы генерирующий псевдослучайную последовательность битов в соответствии с полиномом генератора,

схему перестановки, во время работы принимающую содержание каскадов сдвигового регистра и выполняющую перестановку битов, присутствующих в каскадах регистра в соответствии с кодом перестановки, для формирования адреса одной из поднесущих ОМЧР, и

модуль управления, во время работы, в комбинации со схемой проверки адреса, повторно генерирующий адрес, когда сгенерированный адрес превышает заданный максимальный действительный адрес, отличающееся тем, что

заданный максимальный действительный адрес меньше чем 1024,

линейный сдвиговый регистра с обратной связью имеет девять каскадов регистра с полиномом генератора для линейного сдвигового регистра с обратной связью ![]() , и порядок перестановки формирует с дополнительным битом адреса

, и порядок перестановки формирует с дополнительным битом адреса ![]() из десяти битов для i-го символа данных из бита, присутствующего в n-м каскаде

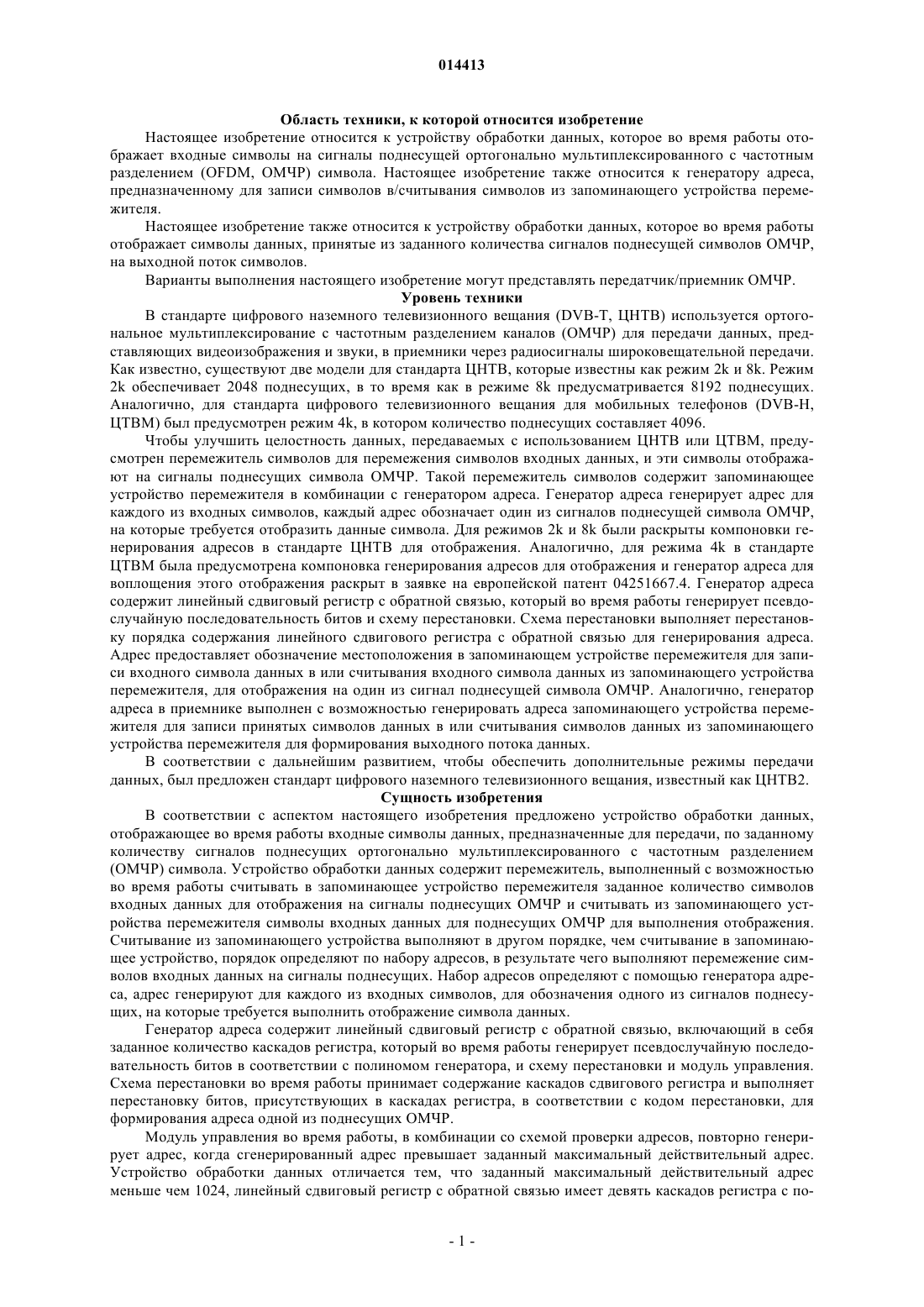

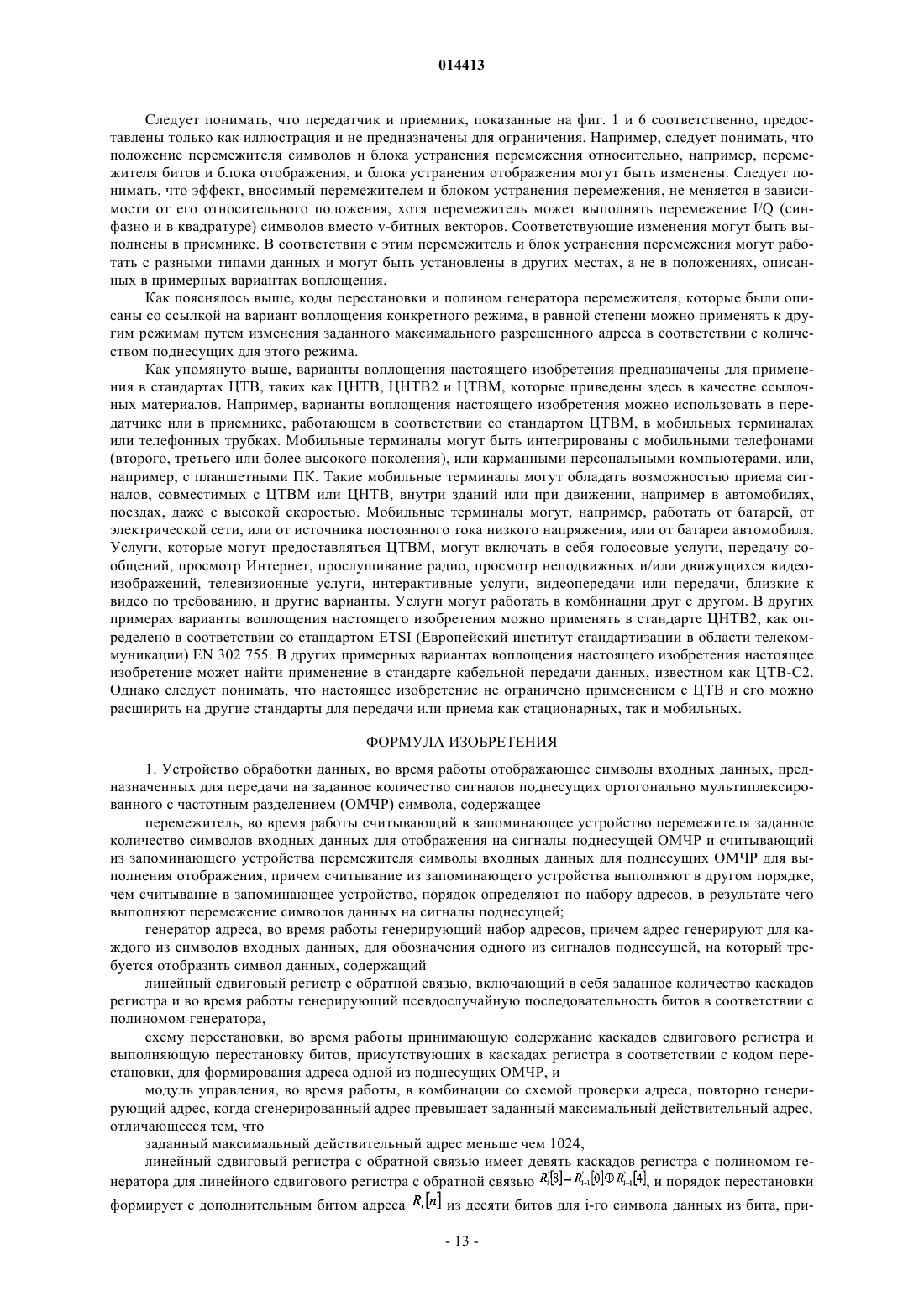

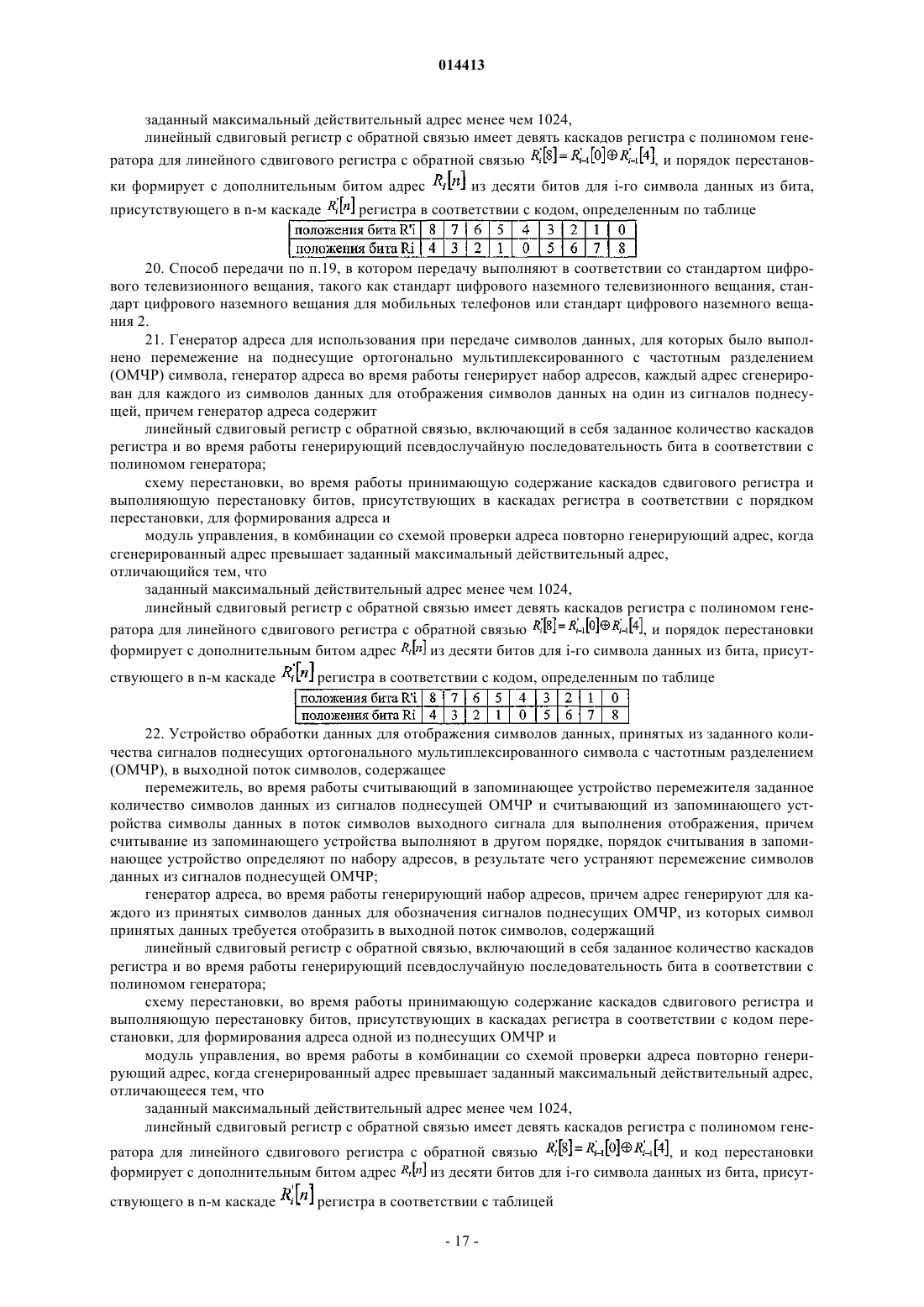

из десяти битов для i-го символа данных из бита, присутствующего в n-м каскаде ![]() регистра в соответствии с кодом, определенным по таблице

регистра в соответствии с кодом, определенным по таблице

![]()

2. Устройство обработки данных по п.1, в котором заданный максимальный действительный адрес представляет собой значение, по существу, между 700 и 1024.

3. Устройство обработки данных по п.1, в котором символ ОМЧР включает в себя пилотные поднесущие, которые выполнены с возможностью переноса известных символов, и заданный максимальный действительный адрес зависит от количества пилотных символов поднесущих, присутствующих в символе ОМЧР.

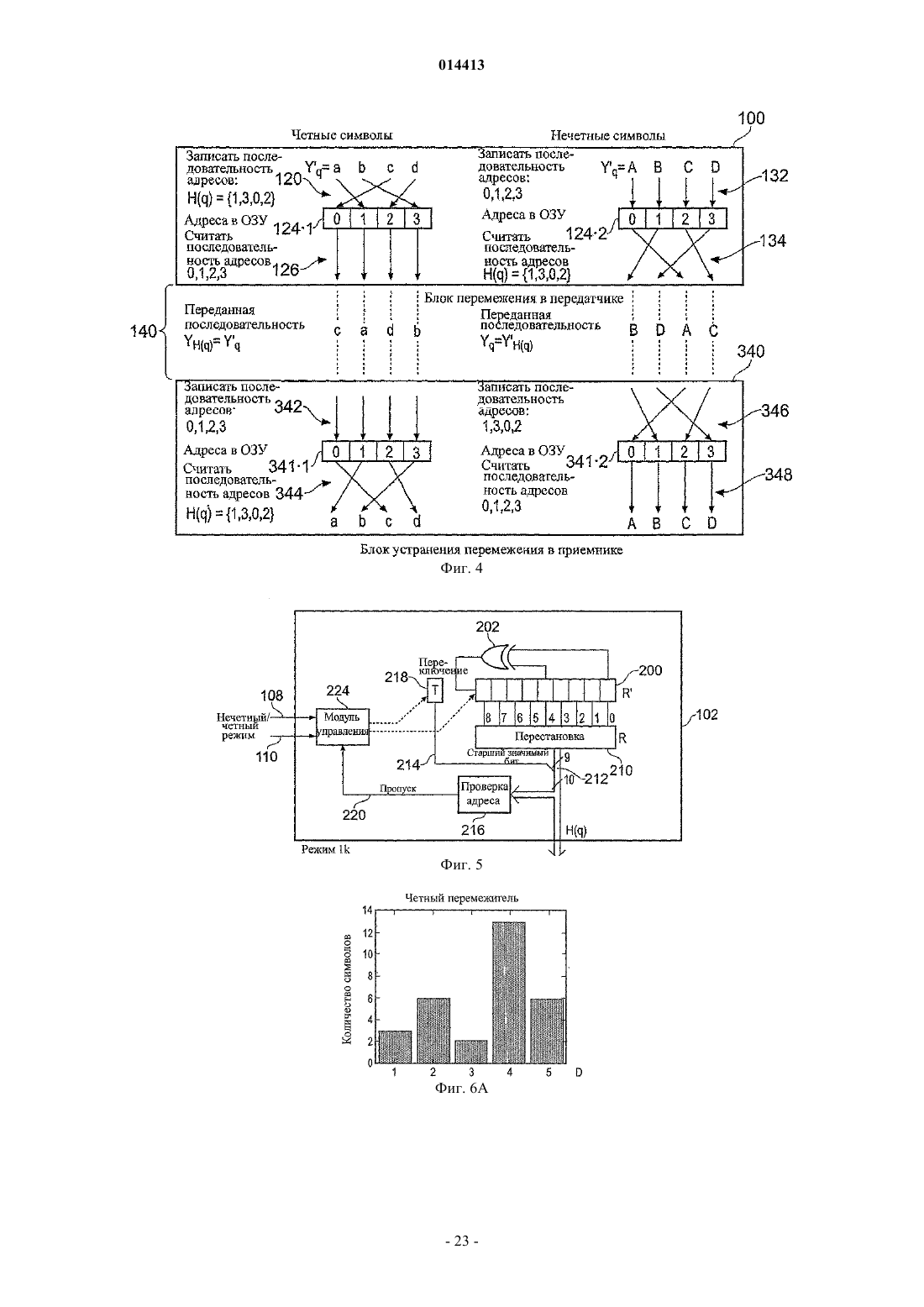

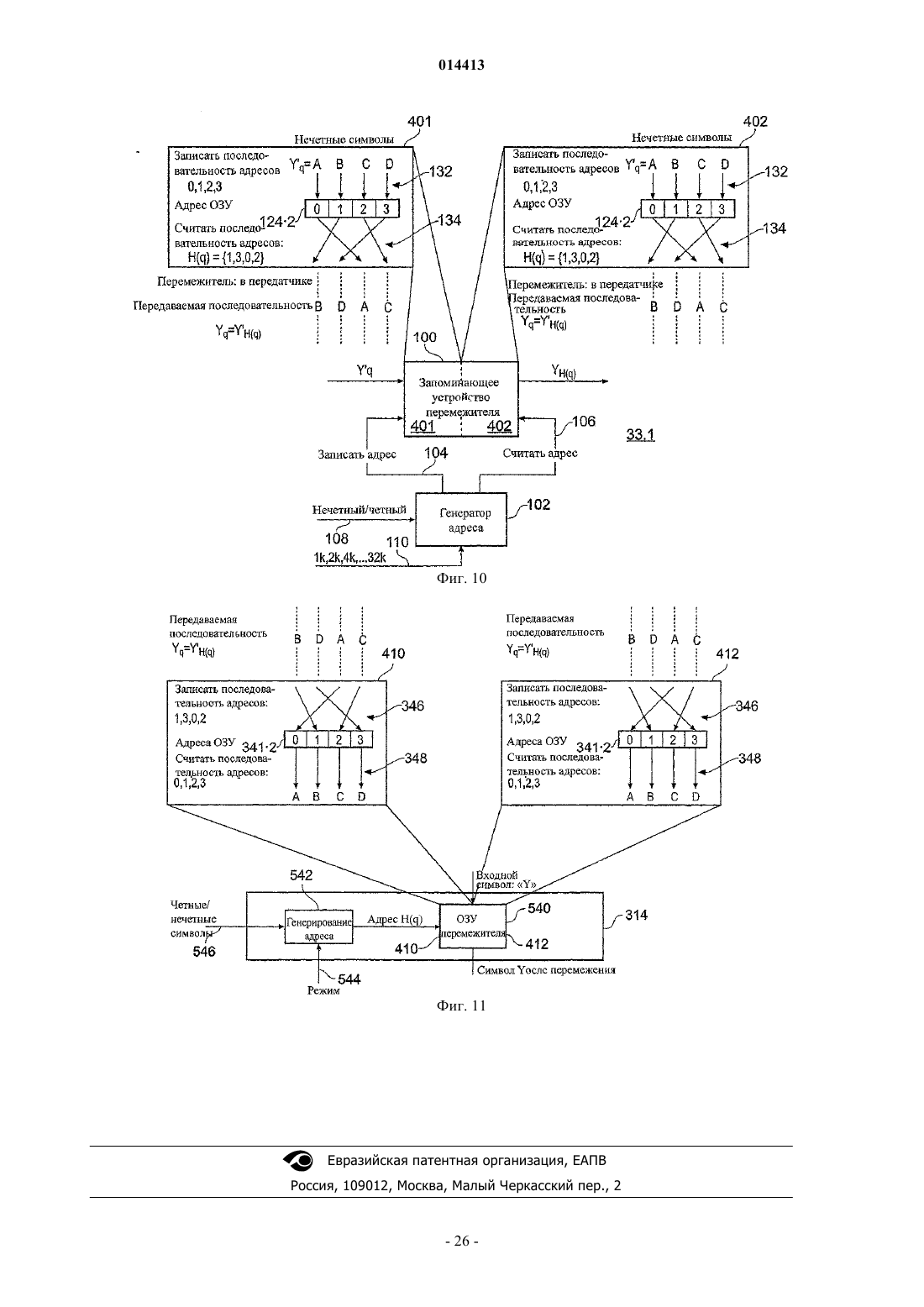

4. Устройство обработки данных по п.1, в котором запоминающее устройство перемежителя во время работы выполняет отображение символов входных данных на сигналы поднесущей для четных символов ОМЧР путем считывания в запоминающее устройство символов данных в соответствии с набором адресов, сгенерированных генератором адреса, и считывания из запоминающего устройства в порядке следования и для нечетных символов ОМЧР путем считывания символов в запоминающее устройство перемежителя в порядке следования и считывания символов данных из запоминающего устройства в соответствии с набором адресов, сгенерированных генератором адреса.

5. Устройство обработки данных по п.1, в котором схема перестановки во время работы изменяет код перестановки, который выполняет перестановку порядка битов каскадов регистра для формирования адресов из одного символа ОМЧР на другой.

6. Устройство обработки данных по п.5, в котором схема перестановки во время работы циклически обрабатывает последовательность разных кодов перестановки для последовательных символов ОМЧР.

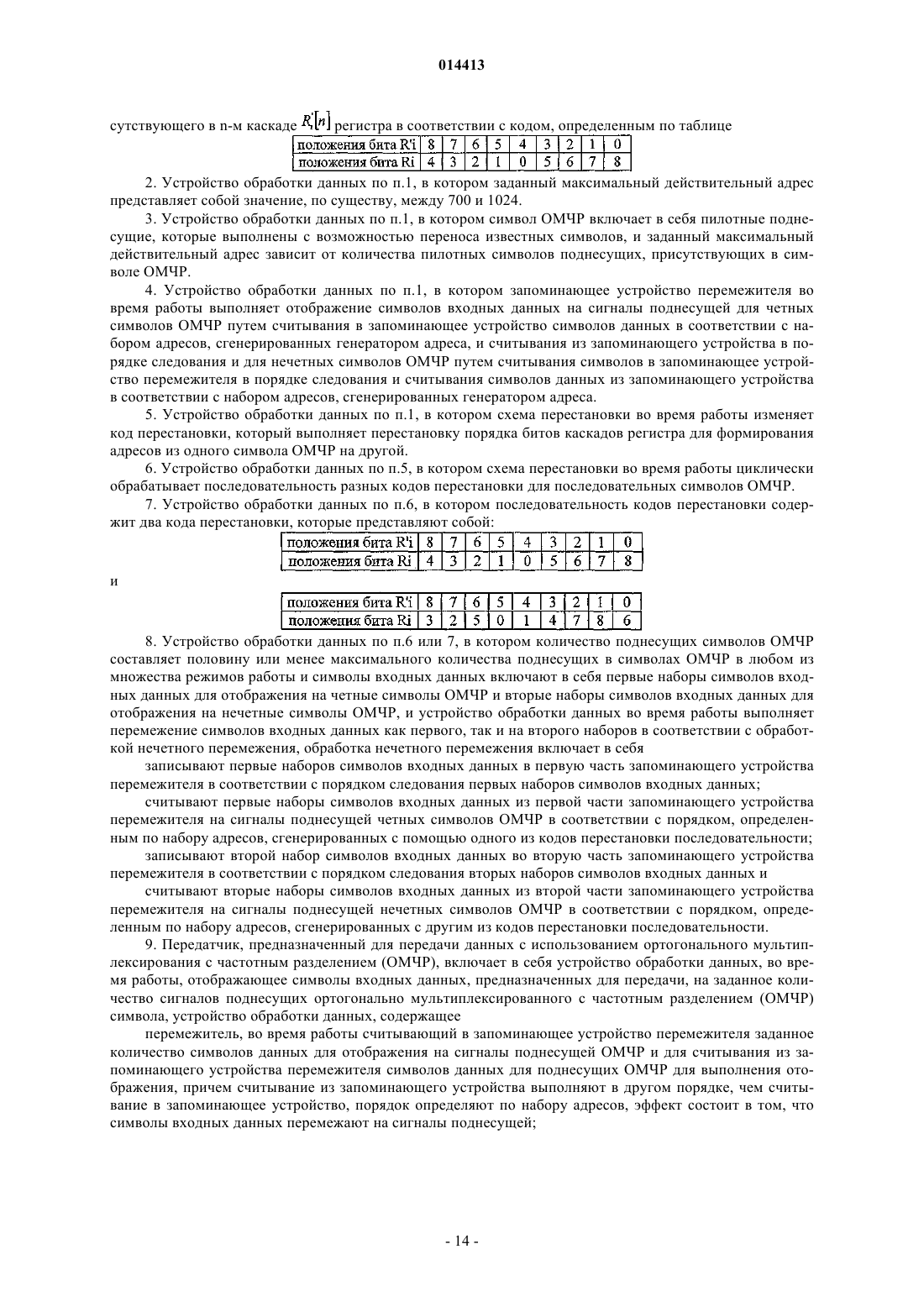

7. Устройство обработки данных по п.6, в котором последовательность кодов перестановки содержит два кода перестановки, которые представляют собой:

![]()

и

![]()

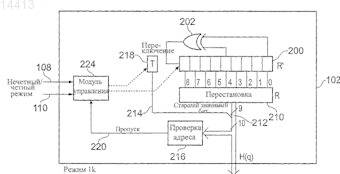

8. Устройство обработки данных по п.6 или 7, в котором количество поднесущих символов ОМЧР составляет половину или менее максимального количества поднесущих в символах ОМЧР в любом из множества режимов работы и символы входных данных включают в себя первые наборы символов входных данных для отображения на четные символы ОМЧР и вторые наборы символов входных данных для отображения на нечетные символы ОМЧР, и устройство обработки данных во время работы выполняет перемежение символов входных данных как первого, так и на второго наборов в соответствии с обработкой нечетного перемежения, обработка нечетного перемежения включает в себя

записывают первые наборов символов входных данных в первую часть запоминающего устройства перемежителя в соответствии с порядком следования первых наборов символов входных данных;

считывают первые наборы символов входных данных из первой части запоминающего устройства перемежителя на сигналы поднесущей четных символов ОМЧР в соответствии с порядком, определенным по набору адресов, сгенерированных с помощью одного из кодов перестановки последовательности;

записывают второй набор символов входных данных во вторую часть запоминающего устройства перемежителя в соответствии с порядком следования вторых наборов символов входных данных и

считывают вторые наборы символов входных данных из второй части запоминающего устройства перемежителя на сигналы поднесущей нечетных символов ОМЧР в соответствии с порядком, определенным по набору адресов, сгенерированных с другим из кодов перестановки последовательности.

9. Передатчик, предназначенный для передачи данных с использованием ортогонального мультиплексирования с частотным разделением (ОМЧР), включает в себя устройство обработки данных, во время работы, отображающее символы входных данных, предназначенных для передачи, на заданное количество сигналов поднесущих ортогонально мультиплексированного с частотным разделением (ОМЧР) символа, устройство обработки данных, содержащее

перемежитель, во время работы считывающий в запоминающее устройство перемежителя заданное количество символов данных для отображения на сигналы поднесущей ОМЧР и для считывания из запоминающего устройства перемежителя символов данных для поднесущих ОМЧР для выполнения отображения, причем считывание из запоминающего устройства выполняют в другом порядке, чем считывание в запоминающее устройство, порядок определяют по набору адресов, эффект состоит в том, что символы входных данных перемежают на сигналы поднесущей;

генератор адреса, во время работы генерирующий набор адресов, адрес генерируют для каждого из символов входных данных для обозначения одного из сигналов поднесущей, на который символ данных следует отобразить, содержащий

линейный сдвиговый регистр с обратной связью, включающий в себя заданное количество каскадов регистра и во время работы генерирующий псевдослучайную последовательность битов в соответствии с полиномом генератора,

схему перестановки, во время работы принимающую содержание каскадов сдвигового регистра и выполняющую перестановку битов, присутствующих в каскадах регистра в соответствии с кодом перестановки, для формирования адреса одной из поднесущих ОМЧР и

модуль управления, во время работы в комбинации со схемой проверки адреса повторно генерирующий адрес, когда сгенерированный адрес превышает заданный максимальный действительный адрес, отличающийся тем, что

заданный максимальный действительный адрес менее чем 1024,

линейный сдвиговый регистр с обратной связью имеет девять каскадов регистра с полиномом генератора для линейного сдвигового регистра с обратной связью ![]() , и порядок перестановки формирует с дополнительным битом адрес

, и порядок перестановки формирует с дополнительным битом адрес ![]() из десяти битов для i-го символа данных из бита, присутствующего в i-м каскаде

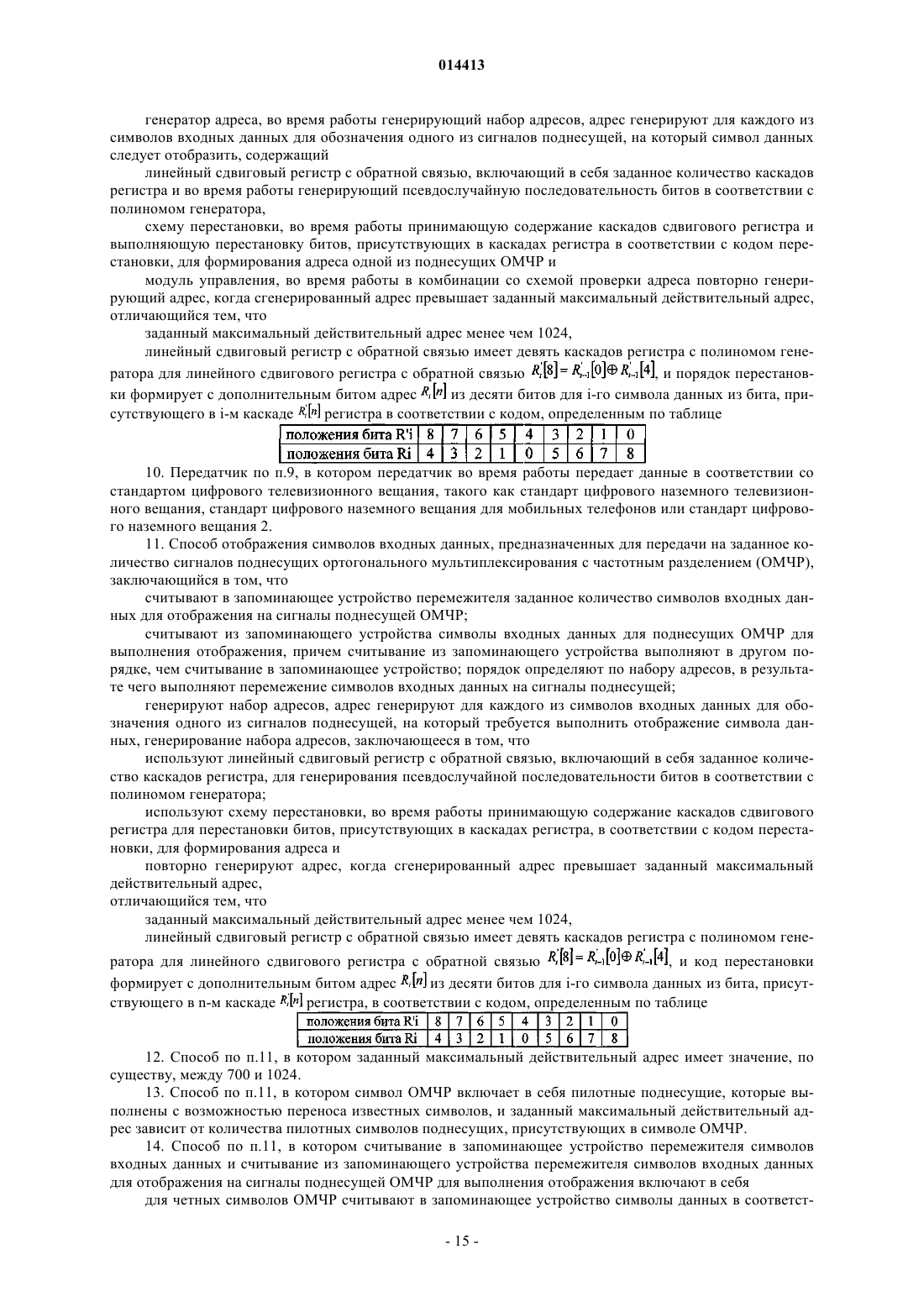

из десяти битов для i-го символа данных из бита, присутствующего в i-м каскаде ![]() регистра в соответствии с кодом, определенным по таблице

регистра в соответствии с кодом, определенным по таблице

![]()

10. Передатчик по п.9, в котором передатчик во время работы передает данные в соответствии со стандартом цифрового телевизионного вещания, такого как стандарт цифрового наземного телевизионного вещания, стандарт цифрового наземного вещания для мобильных телефонов или стандарт цифрового наземного вещания 2.

11. Способ отображения символов входных данных, предназначенных для передачи на заданное количество сигналов поднесущих ортогонального мультиплексирования с частотным разделением (ОМЧР), заключающийся в том, что

считывают в запоминающее устройство перемежителя заданное количество символов входных данных для отображения на сигналы поднесущей ОМЧР;

считывают из запоминающего устройства символы входных данных для поднесущих ОМЧР для выполнения отображения, причем считывание из запоминающего устройства выполняют в другом порядке, чем считывание в запоминающее устройство;

порядок определяют по набору адресов, в результате чего выполняют перемежение символов входных данных на сигналы поднесущей;

генерируют набор адресов, адрес генерируют для каждого из символов входных данных для обозначения одного из сигналов поднесущей, на который требуется выполнить отображение символа данных, генерирование набора адресов, заключающееся в том, что

используют линейный сдвиговый регистр с обратной связью, включающий в себя заданное количество каскадов регистра, для генерирования псевдослучайной последовательности битов в соответствии с полиномом генератора;

используют схему перестановки, во время работы принимающую содержание каскадов сдвигового регистра для перестановки битов, присутствующих в каскадах регистра, в соответствии с кодом перестановки, для формирования адреса и

повторно генерируют адрес, когда сгенерированный адрес превышает заданный максимальный действительный адрес,

отличающийся тем, что

заданный максимальный действительный адрес менее чем 1024,

линейный сдвиговый регистр с обратной связью имеет девять каскадов регистра с полиномом генератора для линейного сдвигового регистра с обратной связью ![]() , и код перестановки формирует с дополнительным битом адрес

, и код перестановки формирует с дополнительным битом адрес ![]() из десяти битов для i-го символа данных из бита, присутствующего в n-м каскаде

из десяти битов для i-го символа данных из бита, присутствующего в n-м каскаде ![]() регистра, в соответствии с кодом, определенным по таблице

регистра, в соответствии с кодом, определенным по таблице

![]()

12. Способ по п.11, в котором заданный максимальный действительный адрес имеет значение, по существу, между 700 и 1024.

13. Способ по п.11, в котором символ ОМЧР включает в себя пилотные поднесущие, которые выполнены с возможностью переноса известных символов, и заданный максимальный действительный адрес зависит от количества пилотных символов поднесущих, присутствующих в символе ОМЧР.

14. Способ по п.11, в котором считывание в запоминающее устройство перемежителя символов входных данных и считывание из запоминающего устройства перемежителя символов входных данных для отображения на сигналы поднесущей ОМЧР для выполнения отображения включают в себя

для четных символов ОМЧР считывают в запоминающее устройство символы данных в соответствии с набором адресов, сгенерированным генератором адреса, и считывают из запоминающего устройства в порядке следования и

для нечетных символов ОМЧР считывают символы в запоминающее устройство перемежителя в порядке следования и считывают символы данных из запоминающего устройства перемежителя в соответствии с набором адресов, сгенерированным генератором адреса.

15. Способ по п.11, в котором использование схемы перестановки для приема содержания каскадов сдвигового регистра и перестановки битов, присутствующих в каскадах регистра в соответствии с кодом перестановки, для формирования адреса, включает в себя изменение кода перестановки, в соответствии с которым выполняют перестановку порядка битов в каскадах регистра для формирования адресов с одного символа ОМЧР на другой.

16. Способ по п.15, в котором изменение кода перестановки, выполняющего перестановку порядка битов каскадов регистра для формирования адресов с одного символа ОМЧР на другой, включает в себя циклическую обработку через последовательность разных кодов перестановки для последовательных символов ОМЧР.

17. Способ по п.16, в котором последовательность кодов перестановки содержит два кода перестановки, которые представляют собой:

![]()

и

![]()

18. Способ по п.16 или 17, в котором количество поднесущих символов ОМЧР составляет половину или менее максимального количества поднесущих в символах ОМЧР любого из множества режимов работы, заключающийся в том, что

разделяют входные символы на первые наборы символов входных данных для отображения на четные символы ОМЧР и вторые наборы символов входных данных для отображения на нечетные символы ОМЧР;

выполняют перемежение символов входных данных как из первого, так и их второго наборов в соответствии с нечетной обработкой перемежения;

записывают первые наборы символов входных данных в первую часть запоминающего устройства перемежителя в соответствии с порядком следования первых наборов символов входных данных;

считывают первые наборы символов входных данных из первой части запоминающего устройства перемежителя на сигналы поднесущей четных символов ОМЧР в соответствии с порядком, определенным по набору адресов, сгенерированных с помощью одного из кодов перестановки последовательности;

записывают второй набор символов входных данных во вторую часть запоминающего устройства перемежителя в соответствии с порядком следования вторых наборов символов входных данных и

считывают вторые наборы символов входных данных из второй части запоминающего устройства перемежителя на сигналы поднесущей нечетных символов ОМЧР в соответствии с порядком, определенным по набору адресов, сгенерированному с другими из кодов перестановки последовательности.

19. Способ передачи символов входных данных через заданное количество сигналов поднесущей ортогонально мультиплексированного с частотным разделением (ОМЧР) символа, заключающийся в том, что

принимают заданное количество символов входных данных для отображения на заданное количество сигналов поднесущих;

считывают в запоминающее устройство перемежителя заданное количество символов данных, предназначенных для отображения на сигналы поднесущей ОМЧР;

считывают из запоминающего устройства перемежителя символы данных для поднесущих ОМЧР для выполнения отображения, причем считывание из запоминающего устройства выполняют в другом порядке, чем считывание в запоминающее устройство, порядок определяют из набора адресов, в результате чего выполняют перемежение символов входных данных на сигналы поднесущей;

генерируют набор адресов, причем адрес генерируют для каждого из символов входных данных для обозначения одного из сигналов поднесущих, на который требуется отобразить символ входных данных, генерирование набора адресов, заключающееся в том, что

используют линейный сдвиговый регистр с обратной связью, включающий в себя заданное количество каскадов регистра для генерирования псевдослучайной последовательности битов в соответствии с полиномом генератора;

используют схему перестановки, во время работы принимающую содержание каскадов сдвигового регистра для выполнения перестановки битов, присутствующих в каскадах регистра, в соответствии с порядком перестановки, для формирования адреса и

повторно генерируют адрес, когда сгенерированный адрес превышает заданный максимальный действительный адрес,

отличающийся тем, что

заданный максимальный действительный адрес менее чем 1024,

линейный сдвиговый регистр с обратной связью имеет девять каскадов регистра с полиномом генератора для линейного сдвигового регистра с обратной связью ![]() , и порядок перестановки формирует с дополнительным битом адрес

, и порядок перестановки формирует с дополнительным битом адрес ![]() из десяти битов для i-го символа данных из бита, присутствующего в n-м каскаде

из десяти битов для i-го символа данных из бита, присутствующего в n-м каскаде ![]() регистра в соответствии с кодом, определенным по таблице

регистра в соответствии с кодом, определенным по таблице

![]()

20. Способ передачи по п.19, в котором передачу выполняют в соответствии со стандартом цифрового телевизионного вещания, такого как стандарт цифрового наземного телевизионного вещания, стандарт цифрового наземного вещания для мобильных телефонов или стандарт цифрового наземного вещания 2.

21. Генератор адреса для использования при передаче символов данных, для которых было выполнено перемежение на поднесущие ортогонально мультиплексированного с частотным разделением (ОМЧР) символа, генератор адреса во время работы генерирует набор адресов, каждый адрес сгенерирован для каждого из символов данных для отображения символов данных на один из сигналов поднесущей, причем генератор адреса содержит

линейный сдвиговый регистр с обратной связью, включающий в себя заданное количество каскадов регистра и во время работы генерирующий псевдослучайную последовательность бита в соответствии с полиномом генератора;

схему перестановки, во время работы принимающую содержание каскадов сдвигового регистра и выполняющую перестановку битов, присутствующих в каскадах регистра в соответствии с порядком перестановки, для формирования адреса и

модуль управления, в комбинации со схемой проверки адреса повторно генерирующий адрес, когда сгенерированный адрес превышает заданный максимальный действительный адрес,

отличающийся тем, что

заданный максимальный действительный адрес менее чем 1024,

линейный сдвиговый регистр с обратной связью имеет девять каскадов регистра с полиномом генератора для линейного сдвигового регистра с обратной связью ![]() , и порядок перестановки формирует с дополнительным битом адрес

, и порядок перестановки формирует с дополнительным битом адрес ![]() из десяти битов для i-го символа данных из бита, присутствующего в n-м каскаде

из десяти битов для i-го символа данных из бита, присутствующего в n-м каскаде ![]() регистра в соответствии с кодом, определенным по таблице

регистра в соответствии с кодом, определенным по таблице

![]()

22. Устройство обработки данных для отображения символов данных, принятых из заданного количества сигналов поднесущих ортогонального мультиплексированного символа с частотным разделением (ОМЧР), в выходной поток символов, содержащее

перемежитель, во время работы считывающий в запоминающее устройство перемежителя заданное количество символов данных из сигналов поднесущей ОМЧР и считывающий из запоминающего устройства символы данных в поток символов выходного сигнала для выполнения отображения, причем считывание из запоминающего устройства выполняют в другом порядке, порядок считывания в запоминающее устройство определяют по набору адресов, в результате чего устраняют перемежение символов данных из сигналов поднесущей ОМЧР;

генератор адреса, во время работы генерирующий набор адресов, причем адрес генерируют для каждого из принятых символов данных для обозначения сигналов поднесущих ОМЧР, из которых символ принятых данных требуется отобразить в выходной поток символов, содержащий

линейный сдвиговый регистр с обратной связью, включающий в себя заданное количество каскадов регистра и во время работы генерирующий псевдослучайную последовательность бита в соответствии с полиномом генератора;

схему перестановки, во время работы принимающую содержание каскадов сдвигового регистра и выполняющую перестановку битов, присутствующих в каскадах регистра в соответствии с кодом перестановки, для формирования адреса одной из поднесущих ОМЧР и

модуль управления, во время работы в комбинации со схемой проверки адреса повторно генерирующий адрес, когда сгенерированный адрес превышает заданный максимальный действительный адрес, отличающееся тем, что

заданный максимальный действительный адрес менее чем 1024,

линейный сдвиговый регистр с обратной связью имеет девять каскадов регистра с полиномом генератора для линейного сдвигового регистра с обратной связью ![]() , и код перестановки формирует с дополнительным битом адрес

, и код перестановки формирует с дополнительным битом адрес ![]() из десяти битов для i-го символа данных из бита, присутствующего в n-м каскаде

из десяти битов для i-го символа данных из бита, присутствующего в n-м каскаде ![]() регистра в соответствии с таблицей

регистра в соответствии с таблицей

![]()

23. Устройство обработки данных по п.22, в котором заданный максимальный действительный адрес имеет значение, по существу, между 700 и 1024.

24. Устройство обработки данных по п.22, в котором символ ОМЧР включает в себя пилотные поднесущие, которые скомпонованы для переноса известных символов, и заданный максимальный действительный адрес зависит от количества пилотных символов поднесущей, присутствующих в символе ОМЧР.

25. Устройство обработки данных по п.22, в котором запоминающее устройство перемежителя выполнено с возможностью выполнения отображения принятых символов данных из сигналов поднесущей в поток выходных данных для четных символов ОМЧР путем считывания в запоминающее устройство символов данных в соответствии с порядком следования и считывания символов данных из запоминающего устройства в соответствии с набором адресов, сгенерированным генератором адреса, и для нечетных символов ОМЧР путем считывания символов в запоминающее устройство в соответствии с набором адресов, сгенерированным генератором адреса и считывания символов данных из запоминающего устройства в соответствии с порядком следования.

26. Устройство обработки данных по п.22, в котором схема перестановки во время работы изменяет код перестановки, на основе которого выполняют перестановку порядка битов каскадов регистра, для формирования адреса с одного символа ОМЧР на другой.

27. Устройство обработки данных по п.26, в котором схема перестановки во время работы циклически использует последовательность разных кодов перестановки для последовательных символов ОМЧР.

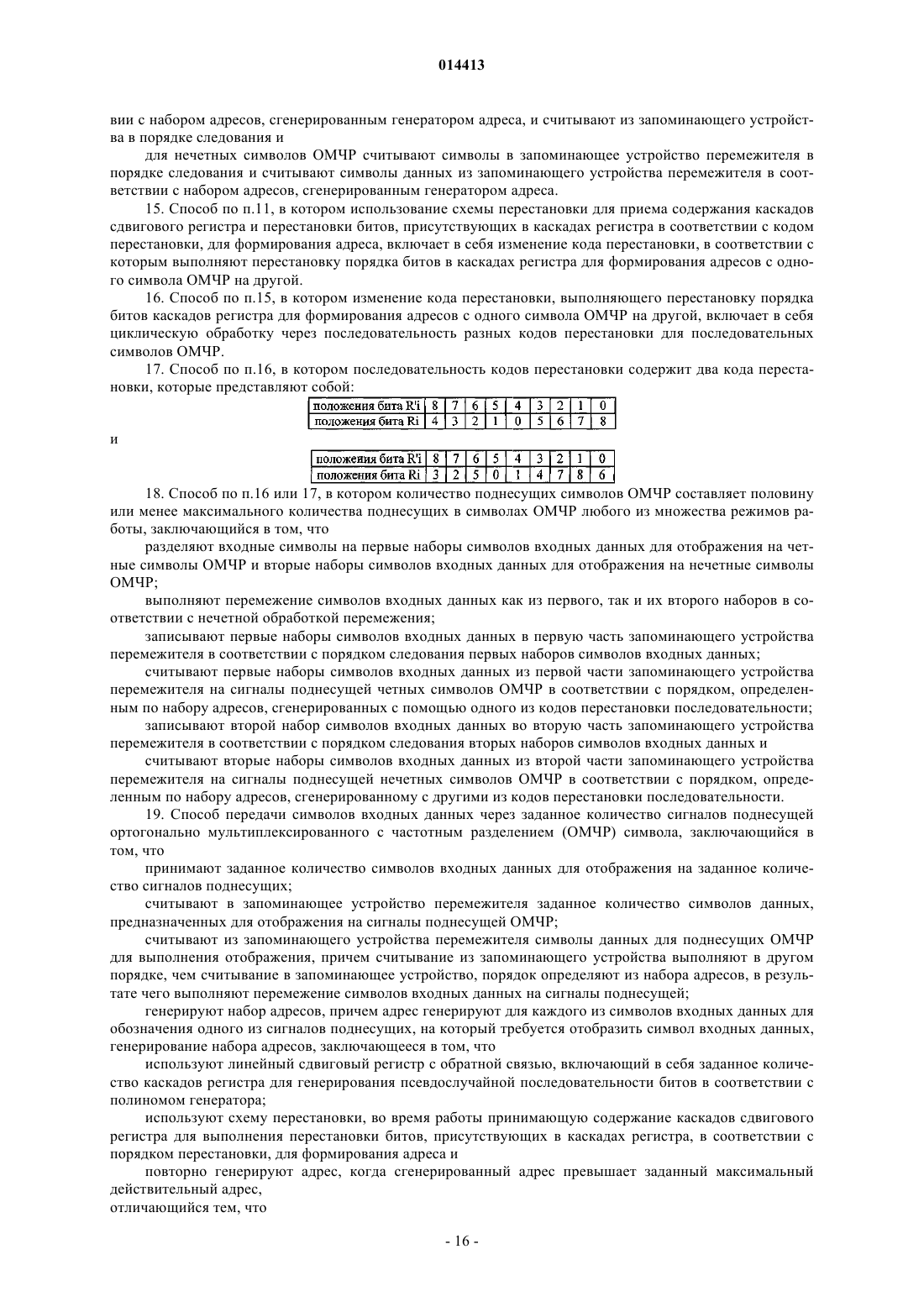

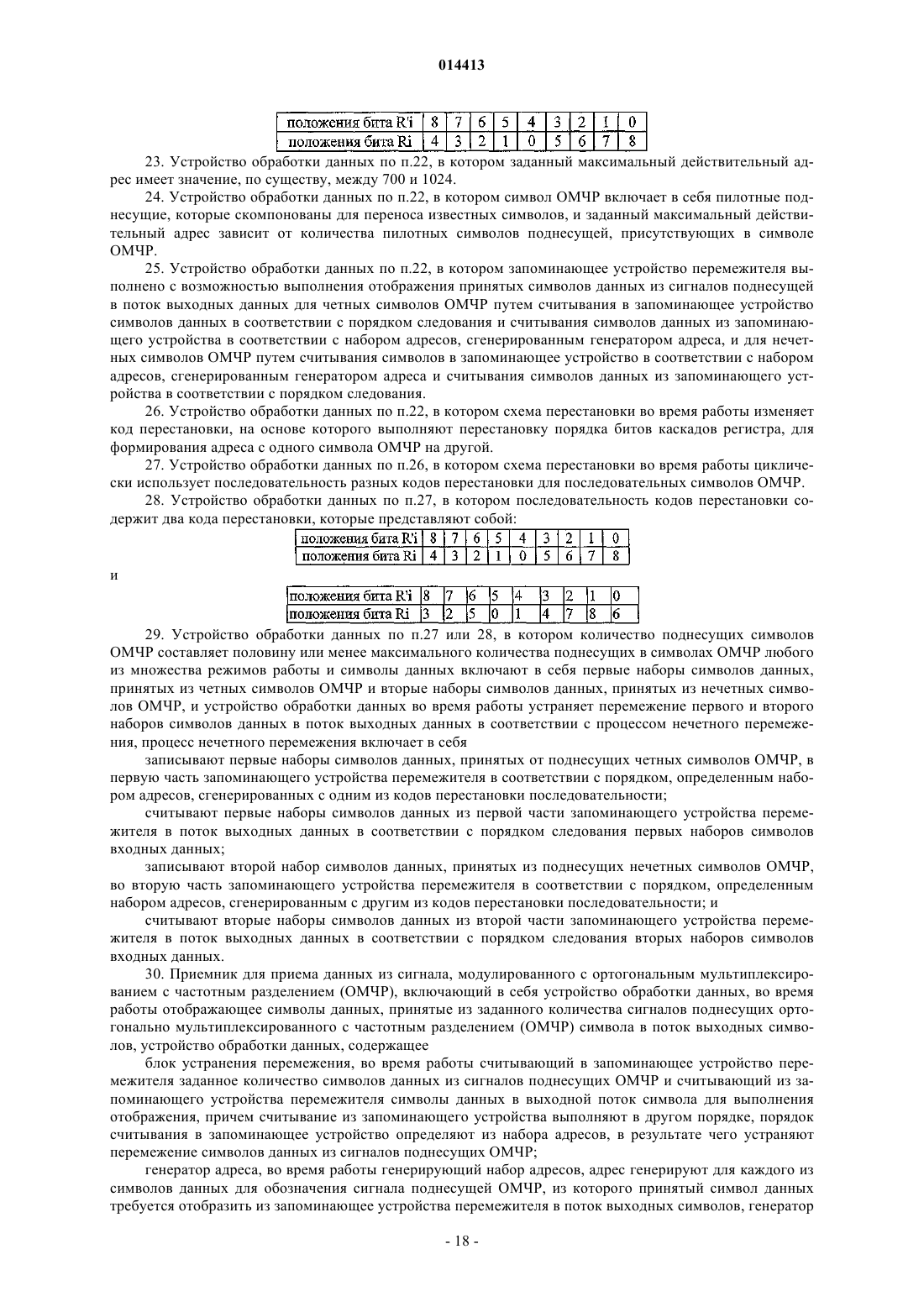

28. Устройство обработки данных по п.27, в котором последовательность кодов перестановки содержит два кода перестановки, которые представляют собой:

![]()

и

![]()

29. Устройство обработки данных по п.27 или 28, в котором количество поднесущих символов ОМЧР составляет половину или менее максимального количества поднесущих в символах ОМЧР любого из множества режимов работы и символы данных включают в себя первые наборы символов данных, принятых из четных символов ОМЧР и вторые наборы символов данных, принятых из нечетных символов ОМЧР, и устройство обработки данных во время работы устраняет перемежение первого и второго наборов символов данных в поток выходных данных в соответствии с процессом нечетного перемежения, процесс нечетного перемежения включает в себя

записывают первые наборы символов данных, принятых от поднесущих четных символов ОМЧР, в первую часть запоминающего устройства перемежителя в соответствии с порядком, определенным набором адресов, сгенерированных с одним из кодов перестановки последовательности;

считывают первые наборы символов данных из первой части запоминающего устройства перемежителя в поток выходных данных в соответствии с порядком следования первых наборов символов входных данных;

записывают второй набор символов данных, принятых из поднесущих нечетных символов ОМЧР, во вторую часть запоминающего устройства перемежителя в соответствии с порядком, определенным набором адресов, сгенерированным с другим из кодов перестановки последовательности; и

считывают вторые наборы символов данных из второй части запоминающего устройства перемежителя в поток выходных данных в соответствии с порядком следования вторых наборов символов входных данных.

30. Приемник для приема данных из сигнала, модулированного с ортогональным мультиплексированием с частотным разделением (ОМЧР), включающий в себя устройство обработки данных, во время работы отображающее символы данных, принятые из заданного количества сигналов поднесущих ортогонально мультиплексированного с частотным разделением (ОМЧР) символа в поток выходных символов, устройство обработки данных, содержащее

блок устранения перемежения, во время работы считывающий в запоминающее устройство перемежителя заданное количество символов данных из сигналов поднесущих ОМЧР и считывающий из запоминающего устройства перемежителя символы данных в выходной поток символа для выполнения отображения, причем считывание из запоминающего устройства выполняют в другом порядке, порядок считывания в запоминающее устройство определяют из набора адресов, в результате чего устраняют перемежение символов данных из сигналов поднесущих ОМЧР;

генератор адреса, во время работы генерирующий набор адресов, адрес генерируют для каждого из символов данных для обозначения сигнала поднесущей ОМЧР, из которого принятый символ данных требуется отобразить из запоминающее устройства перемежителя в поток выходных символов, генератор адреса, содержащий

линейный сдвиговый регистр с обратной связью, включающий в себя заданное количество каскадов регистра и во время работы генерирующий псевдослучайную последовательность битов в соответствии с полиномом генератора;

схему перестановки, во время работы принимающую содержание каскадов сдвигового регистра и выполняющую перестановку битов, присутствующих в каскадах регистра, в соответствии с кодом перестановки, для формирования адреса одной из поднесущих ОМЧР и

модуль управления, во время работы в комбинации со схемой проверки адрес, повторно генерирующий адрес, когда сгенерированный адрес превышает заданный максимальный действительный адрес, отличающийся тем, что

заданный максимальный действительный адрес менее чем 1024,

линейный сдвиговый регистр с обратной связью имеет девять каскадов регистра с полиномом генератора для линейного сдвигового регистра с обратной связью ![]() , и порядок перестановки формирует с дополнительным битом адрес

, и порядок перестановки формирует с дополнительным битом адрес ![]() из десяти битов для i-го символа данных из бита, присутствующего в n-м каскаде

из десяти битов для i-го символа данных из бита, присутствующего в n-м каскаде ![]() регистра в соответствии с таблицей

регистра в соответствии с таблицей

![]()

31. Приемник по п.30, в котором приемник во время работы принимает данные, которые были смодулированы в соответствии со стандартом цифрового телевизионного вещания, такого как стандарт цифрового наземного телевизионного вещания, стандарт цифрового наземного вещания для мобильных телефонов или стандарт цифрового наземного вещания 2.

32. Генератор адреса для использования при приеме символов данных, для которых было выполнено перемежение на поднесущие ортогонально мультиплексированного с частотным разделением (ОМЧР) символа, генератор адреса во время работы генерирует набор адресов, каждый адрес генерируют для каждого из символов данных для обозначения одного из сигналов поднесущей, из которого принятый символ данных требуется отобразить из запоминающего устройства перемежителя в поток выходных данных, генератор адреса, содержащий

линейный сдвиговый регистр с обратной связью, включающий в себя заданное количество каскадов регистра и во время работы генерирующий псевдослучайную последовательность битов в соответствии с полиномом генератора;

схему перестановки, во время работу принимающую содержание каскадов сдвигового регистра и выполняющую перестановку битов, присутствующих в каскадах регистра в соответствии с кодом перестановки, для формирования адреса и

модуль управления, во время работы в комбинации со схемой проверки адреса повторно генерирующий адрес, когда сгенерированный адрес превышает заданный максимальный действительный адрес, отличающийся тем, что

заданный максимальный действительный адрес менее чем 1024,

линейный сдвиговый регистр с обратной связью имеет девять каскадов регистра с полиномом генератора для линейного сдвигового регистра с обратной связью ![]() , и порядок перестановки формирует с дополнительным битом адрес

, и порядок перестановки формирует с дополнительным битом адрес ![]() из десяти битов для i-го символа данных из бита, присутствующего в n-м каскаде

из десяти битов для i-го символа данных из бита, присутствующего в n-м каскаде ![]() регистра в соответствии с кодом, определенным по таблице

регистра в соответствии с кодом, определенным по таблице

![]()

33. Способ отображения символов, принятых из заданного количества сигналов поднесущих ортогонально мультиплексированного с частотным разделением (ОМЧР) символа в выходной поток символов, содержащий

считывают в запоминающее устройство перемежителя заданное количество символов данных из сигналов поднесущих ОМЧР;

считывают из запоминающего устройства перемежителя символы данных в выходной поток символов для выполнения отображения, причем считывание из запоминающего устройства выполняют в другом порядке, чем считывание в запоминающее устройство, порядок определяют из набора адресов, в результате чего устраняют перемежение символов данных из сигналов поднесущих ОМЧР;

генерируют набор адресов, адрес генерируют для каждого из принятых символов данных для обозначения сигнала поднесущей ОМЧР, из которого принятый символ данных требуется отобразить из запоминающего устройства перемежителя в выходной поток символов, генерирование набора адресов содержит

линейный сдвиговый регистр с обратной связью, включающий в себя заданное количество каскадов регистра, для генерирования псевдослучайной последовательности битов в соответствии с полиномом генератора;

схему перестановки для приема содержания каскадов сдвигового регистра и для перестановки битов, присутствующих в каскадах регистра, в соответствии с кодом перестановки для формирования адреса и

повторно генерируют адрес, когда сгенерированный адрес превышает заданный максимальный действительный адрес,

отличающийся тем, что

заданный максимальный действительный адрес менее чем 1024,

линейный сдвиговый регистр с обратной связью имеет девять каскадов регистра с полиномом генератора для линейного сдвигового регистра с обратной связью ![]() , и порядок перестановки формирует с дополнительным битом адрес

, и порядок перестановки формирует с дополнительным битом адрес ![]() из десяти битов для i-го символа данных из бита, присутствующего в n-м каскаде

из десяти битов для i-го символа данных из бита, присутствующего в n-м каскаде ![]() регистра в соответствии с таблицей

регистра в соответствии с таблицей

![]()

34. Способ по п.33, в котором заданный максимальный действительный адрес представляет собой значение, по существу, между 700 и 1024.

35. Способ по п.33, в котором символ ОМЧР включает в себя пилотные поднесущие, которые выполнены с возможностью переноса известных символов, и заданный максимальный действительный адрес зависит от количества пилотных символов поднесущей, присутствующих в символе ОМЧР.

36. Способ по п.33, в котором считывание в запоминающее устройство перемежителя заданного количества символов данных из сигналов поднесущей ОМЧР и считывание из запоминающего устройства перемежителя символов данных в выходной поток символов для выполнения отображения включают в себя

для четных символов ОМЧР считывают в запоминающее устройство символы данных в соответствии с порядком следования и считывают символы данных из запоминающего устройства перемежителя в соответствии с набором адресов, генерируемых генератором адреса; и

для нечетных символов ОМЧР считывают символы данных в запоминающее устройство перемежителя в соответствии с набором адресов, генерируемым генератором адреса, и считывают символы данных из запоминающего устройства в соответствии с порядком следования.

37. Способ по п.33, в котором использование схемы перестановки для приема содержания каскадов сдвигового регистра и перестановки битов, присутствующих в каскадах регистра в соответствии с кодом перестановки для формирования адреса, включает в себя изменение кода перестановки, на основе которого выполняют перестановку порядка битов каскадов регистра, для формирования адресов с одного символа ОМЧР на другой.

38. Способ по п.37, в котором изменение кода перестановки, на основе которого выполняют перестановку порядка битов каскадов сдвигового регистра для формирования адресов с одного символа ОМЧР на другой, включает в себя циклическую обработку через последовательность разных кодов перестановки для последовательных символов ОМЧР.

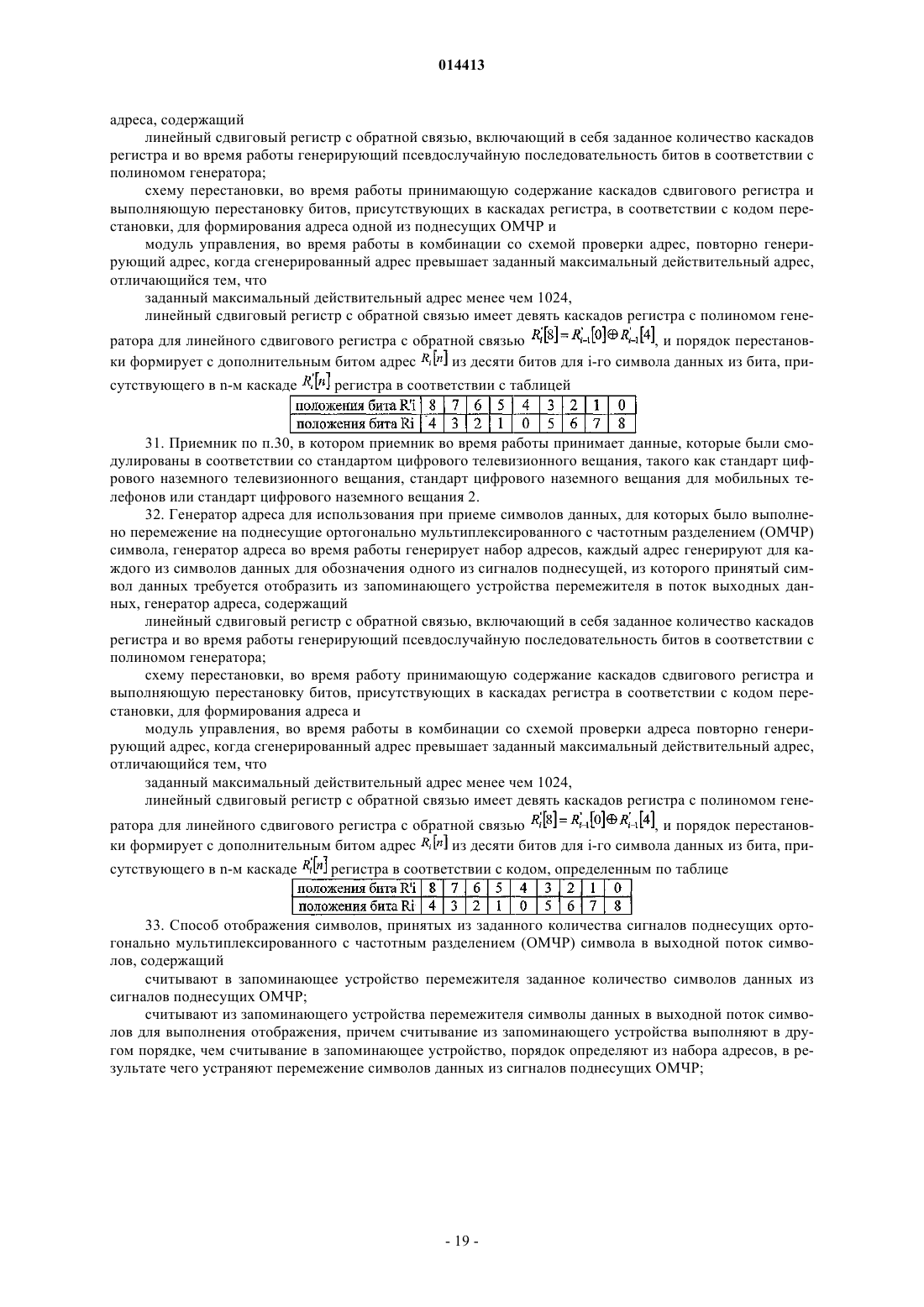

39. Способ по п.38, в котором последовательность кодов перестановки содержит два кода перестановки, которые представляют собой:

![]()

и

![]()

40. Способ по п.37, в котором количество поднесущих символов ОМЧР составляет половину или менее максимального количества поднесущих в символах ОМЧР любого из множества режимов работы, заключающийся в том, что

принимают первые наборы символов данных из четных символов ОМЧР и вторые наборы символов данных из нечетных символов ОМЧР, и считывают в запоминающее устройство перемежителя символы данных, принятые из сигналов поднесущих ОМЧР, и считывают из запоминающего устройства перемежителя символы данных в выходной поток символов для выполнения отображения в соответствии с процессом нечетного перемежения, который включает в себя следующее:

записывают первые наборы символов данных, принятых из сигналов поднесущих четных символов ОМЧР, в первую часть запоминающего устройства перемежителя в соответствии с порядком, определенным по набору адресов, сгенерированных с одним из кодов перестановки последовательности;

считывают первые наборы символов данных из первой части запоминающего устройства перемежителя в выходной поток данных в соответствии с порядком следования первых наборов символов входных данных;

записывают второй набор символов данных, принятых из поднесущих нечетных символов ОМЧР, во вторую часть запоминающего устройства перемежителя в соответствии с порядком, определенным по набору адресов, сгенерированных с другим из кодов перестановки последовательности, и

считывают вторые наборы символов данных из второй части запоминающего устройства перемежителя в выходной поток данных в соответствии с порядком следования вторых наборов символов входных данных.

41. Способ приема данных из символов, модулированных с ортогональным мультиплексированием с частотным разделением ОМЧР, заключающийся в том, что

принимают заданное количество символов данных из заданного количества сигналов поднесущей из символов ОМЧР для формирования выходного потока данных;

считывают в запоминающее устройство перемежителя заданное количество символов данных из сигналов поднесущей ОМЧР;

считывают из запоминающего устройства перемежителя символы данных в выходной поток символов для выполнения отображения, причем считывание из запоминающего устройства выполняют в другом порядке, чем считывание в запоминающее устройство, порядок определяют из набора адресов, в результате устраняют перемежение символов данных из сигналов поднесущих ОМЧР;

генерируют набор адресов, причем адрес генерируют для каждого из принятых символов для обозначения сигнала поднесущей ОМЧР, из которого принятый символ данных требуется отобразить в выходной поток символов, генерирование набора адресов, заключающееся в том, что

используют линейный сдвиговый регистр с обратной связью, включающий в себя заданное количество каскадов регистра, для генерирования псевдослучайной последовательности битов в соответствии с полиномом генератора;

используют схему перестановки для приема содержания каскадов сдвигового регистра и выполнения перестановки битов, присутствующих в каскадах регистра, в соответствии с кодом перестановки для формирования адреса и

повторно генерируют адрес, когда сгенерированный адрес превышает заданный максимальный действительный адрес,

отличающийся тем, что

заданный максимальный действительный адрес менее чем 1024,

линейный сдвиговый регистр с обратной связью имеет девять каскадов регистра с полиномом генератора для линейного сдвигового регистра с обратной связью ![]() , и порядок перестановки формирует с дополнительным битом адрес

, и порядок перестановки формирует с дополнительным битом адрес ![]() из десяти битов для i-го символа данных из бита, присутствующего в n-м каскаде

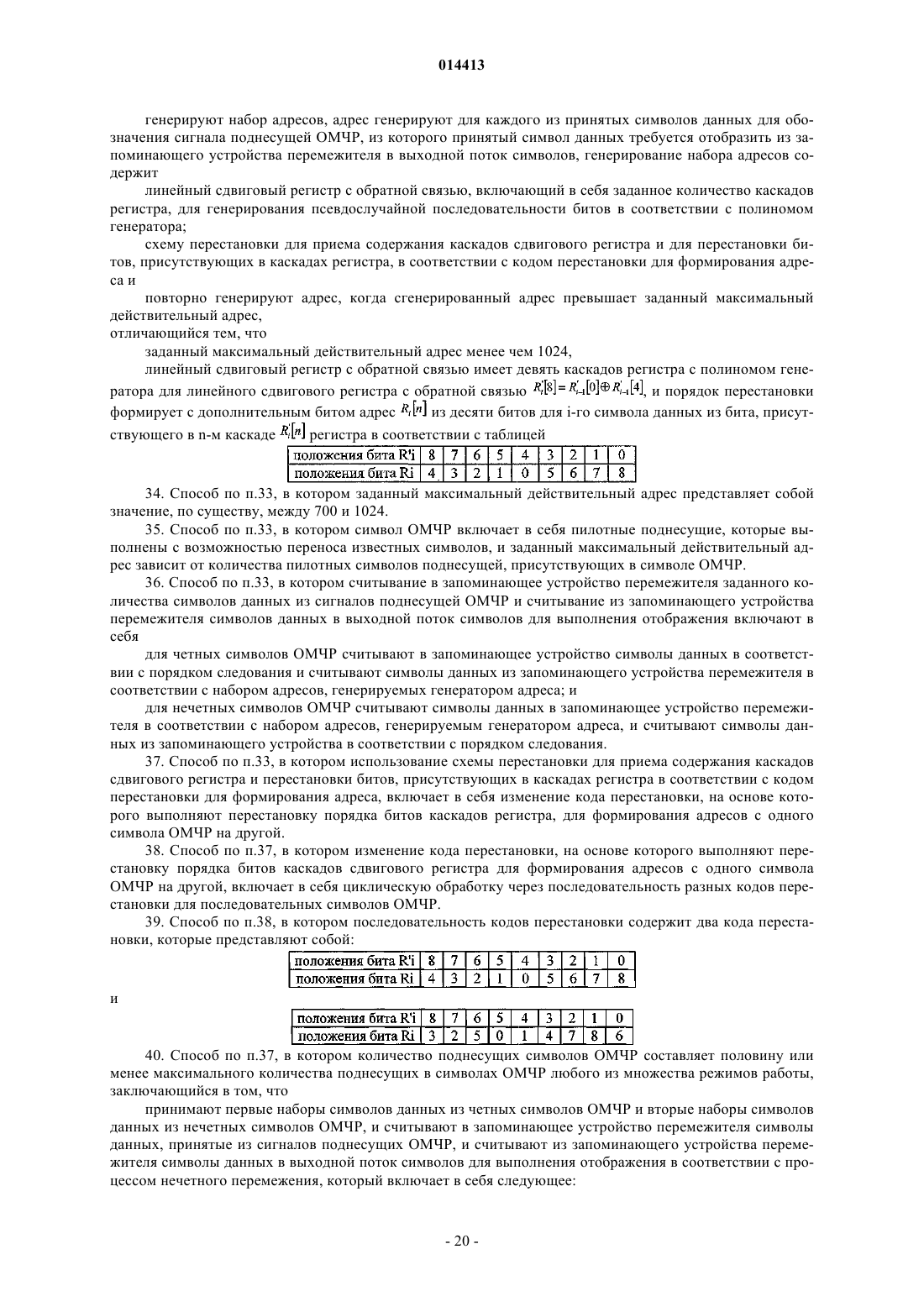

из десяти битов для i-го символа данных из бита, присутствующего в n-м каскаде ![]() в регистра соответствии с кодом, определенным по таблице

в регистра соответствии с кодом, определенным по таблице

![]()

42. Способ приема по п.40, в котором прием символов данных из сигналов поднесущей символов ОМЧР выполняют в соответствии со стандартом цифрового телевизионного вещания, такого как стандарт цифрового наземного телевизионного вещания, стандарт цифрового наземного вещания для мобильных телефонов или стандарт цифрового наземного вещания 2.

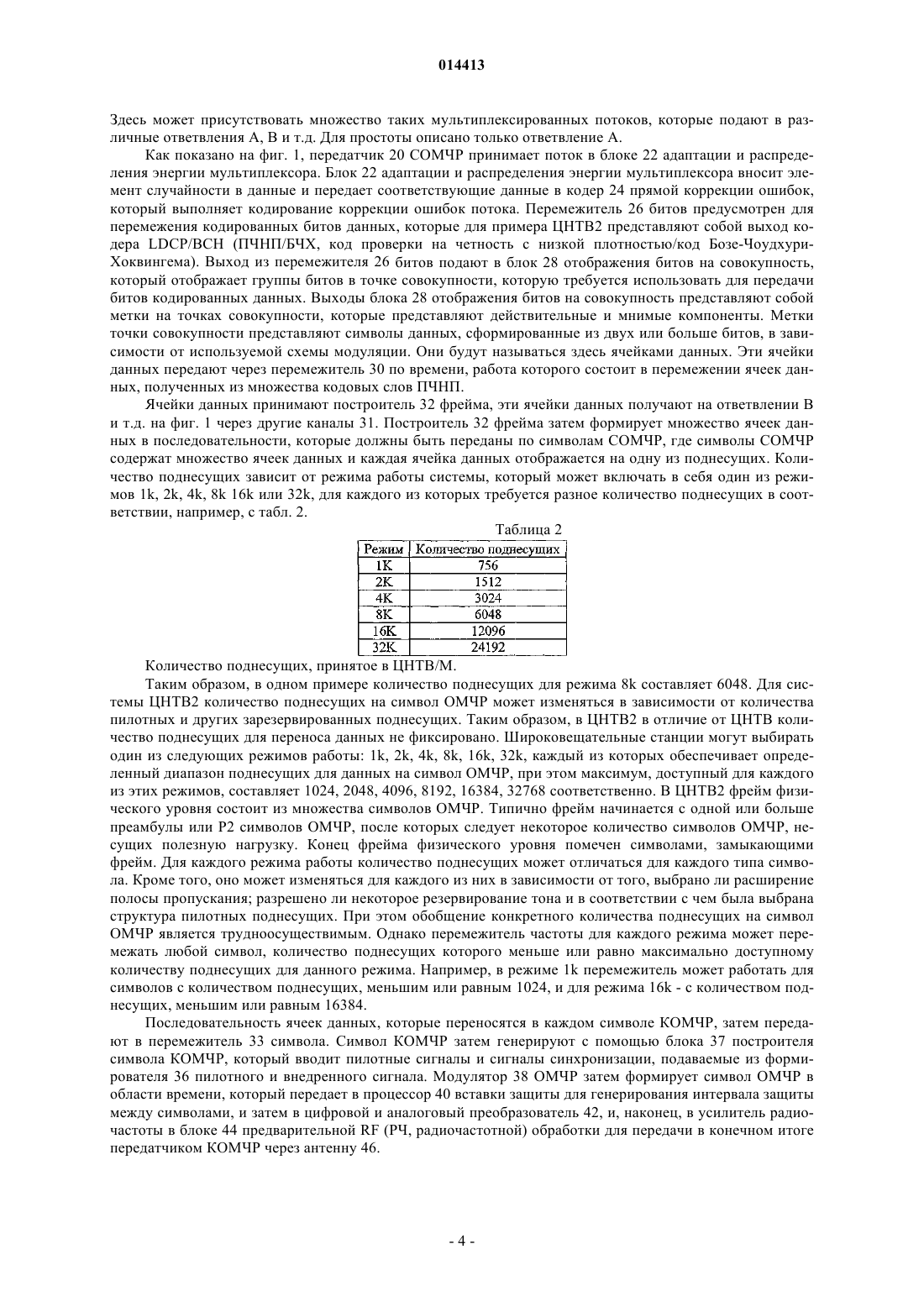

Текст