Схема умножения для устройства измерения мощности и способ измерения мгновенного значения мощности

Номер патента: 1361

Опубликовано: 26.02.2001

Авторы: Кроснов Михаил Николаевич, Кузюкин Алексей Михайлович

Формула / Реферат

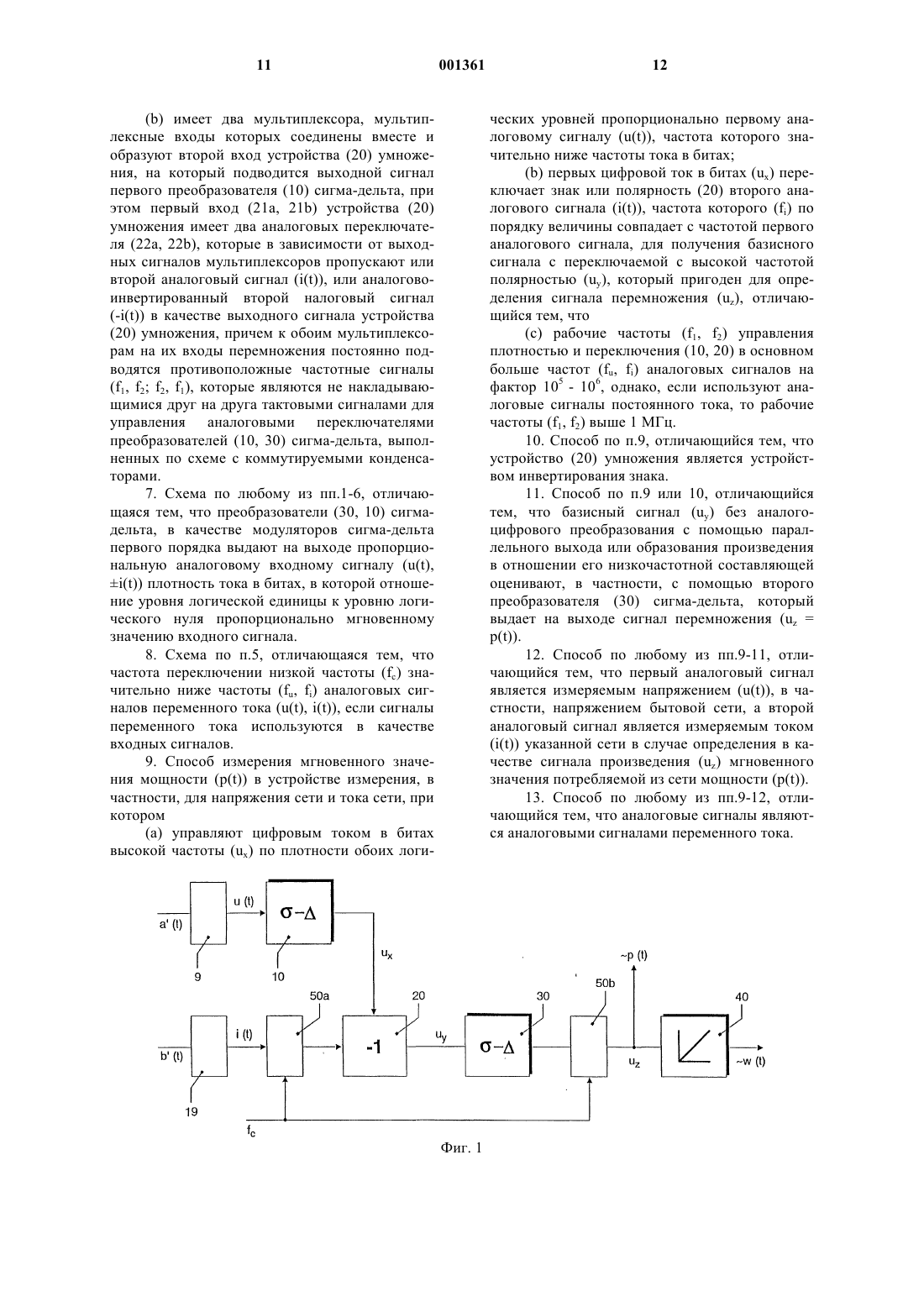

1. Схема умножения для устройства измерения мощности или энергии (Р, W, 30, 40), содержащая

(a) первый преобразователь (SDM1; 10) сигма-дельта, на вход которого подается первый измеряемый аналоговый сигнал (9) (u(t)), а его выход управляет устройством (20; 20а, 20b, 20с, 20d; 21f, 21b, 22а, 22b) умножения, при этом

(b) на устройство (20) умножения подается второй измеряемый сигнал (19) (i(t)), a

(c) выход устройства (20) умножения соединен со вторым преобразователем (SDM2; 30) сигма-дельта, на выходе которого создается выходной сигнал (p(t)), который представляет произведение первого и второго аналоговых сигналов (u(t), i(t)), отличающаяся тем, что

(d) перед устройством (20) умножения и соответственно после второго преобразователя (30) сигма-дельта расположено по одной цифровой инвертирующей ступени (50а, 50b), которые синхронно управляются по низкой частоте (fс), причем

(e) рабочая частота преобразователей (10, 30) сигма-дельта выбрана в МГц-диапазоне, частоты аналоговых сигналов переменного тока (fu, fi) выбраны в диапазоне 20-1000 Гц, а частота переключения цифровых инвертирующих ступеней составляет менее 10 Гц, чтобы для измерения выходного сигнала (p(t)) обеспечить работу обоих преобразователей (10, 30) сигма-дельта и компенсацию их смещения с одной частотой значительно выше и соответственно с другой частотой явно ниже частот измеряемых аналоговых сигналов.

2. Схема по п.1, отличающаяся тем, что

(a) действующее значение первого сигнала (u(t)) меньше изменяющегося сигнала переменного тока, в частности, сигнала, представляющего напряжение сети (uNetz(t)), и

(b) действующее значение второго сигнала (i(t)) значительно сильнее изменяющегося сигнала переменного тока, в частности, сигнала, представляющего ток сети (iNetz(t)).

3. Схема по п.2, отличающаяся тем, что напряжение сети и ток сети измеряются от уровня 110, 220 или 380 В.

4. Схема по любому из пп.1-3, отличающаяся тем, что выходной сигнал (p(t)) подается на аналоговый или цифровой интегратор (40), в частности реверсивный счетчик, счетные ступени которого выполнены с возможностью считывания, по меньшей мере, одного периода, предпочтительно двух и более периодов аналоговых сигналов переменного тока (u(t), i(t)), и считывания бинарного выходного сигнала второго преобразователя (30) сигма-дельта без переполнения, так что выход интегратора (40) непрерывно представляет работу (w(t)), выполненную обоими аналоговыми сигналами.

5. Схема по любому из пп.1-4, отличающаяся тем, что первая и вторая цифровые инвертирующие ступени (50а, 50b) являются схемами "исключающего ИЛИ".

6. Схема по любому из пп.1-5, отличающаяся тем, что устройство (20) умножения имеет два выхода и

(а) содержит четыре аналоговых переключателя (20а, 20b, 20с, 20d), включенных по мостовой схеме, причем плечо моста является выходом, а верхний и соответственно нижний конец моста являются первым входом устройства (20) умножения, причем второй вход устройства (20) умножения является цифровым входом, который одновременно замыкает и одновременно размыкает два соответствующих аналоговых переключателя (20f, 20d; 20b, 20с), при этом одновременно замыкаемые или одновременно размыкаемые аналоговые переключатели являются соответственно одним верхним аналоговым переключателем одной половины моста и одним нижним аналоговым переключателем другой половины моста, чтобы независимо от выходного сигнала (ux) первого преобразователя (10) сигма-дельта приводить в действие аналоговые переключатели и передавать второй аналоговый сигнал (i(t)) в соответствии с положением переключения аналоговых переключателей непосредственно или с инвертированной полярностью; или

(b) имеет два мультиплексора, мультиплексные входы которых соединены вместе и образуют второй вход устройства (20) умножения, на который подводится выходной сигнал первого преобразователя (10) сигма-дельта, при этом первый вход (21а, 21b) устройства (20) умножения имеет два аналоговых переключателя (22а, 22b), которые в зависимости от выходных сигналов мультиплексоров пропускают или второй аналоговый сигнал (i(t)), или аналогово-инвертированный второй аналоговый сигнал (-i(t)) в качестве выходного сигнала устройства (20) умножения, причем к обоим мультиплексорам на их входы перемножения постоянно подводятся противоположные частотные сигналы (f1, f2; f2, f1), которые являются не накладывающимися друг на друга тактовыми сигналами для управления аналоговыми переключателями преобразователей (10, 30) сигма-дельта, выполненных по схеме с коммутируемыми конденсаторами.

7. Схема по любому из пп.1-6, отличающаяся тем, что преобразователи (30, 10) сигма-дельта, в качестве модуляторов сигма-дельта первого порядка выдают на выходе пропорциональную аналоговому входному сигналу (u(t), +i(t)) плотность тока в битах, в которой отношение уровня логической единицы к уровню логического нуля пропорционально мгновенному значению входного сигнала.

8. Схема по п.5, отличающаяся тем, что частота переключении низкой частоты (fс) значительно ниже частоты (fu, fi) аналоговых сигналов переменного тока (u(t), i(t)), если сигналы переменного тока используются в качестве входных сигналов.

9. Способ измерения мгновенного значения мощности (p(t)) в устройстве измерения, в частности, для напряжения сети и тока сети, при котором

(a) управляют цифровым током в битах высокой частоты (ux) по плотности обоих логических уровней пропорционально первому аналоговому сигналу (u(t)), частота которого значительно ниже частоты тока в битах;

(b) первых цифровой ток в битах (ux) переключает знак или полярность (20) второго аналогового сигнала (i(t)), частота которого (fi) по порядку величины совпадает с частотой первого аналогового сигнала, для получения базисного сигнала с переключаемой с высокой частотой полярностью (uy), который пригоден для определения сигнала перемножения (uz), отличающийся тем, что

(c) рабочие частоты (f1, f2) управления плотностью и переключения (10, 20) в основном больше частот (fu, fi) аналоговых сигналов на фактор 105 - 106, однако, если используют аналоговые сигналы постоянного тока, то рабочие частоты (f1, f2) выше 1 МГц.

10. Способ по п.9, отличающийся тем, что устройство (20) умножения является устройством инвертирования знака.

11. Способ по п.9 или 10, отличающийся тем, что базисный сигнал (uy) без аналого-цифрового преобразования с помощью параллельного выхода или образования произведения в отношении его низкочастотной составляющей оценивают, в частности, с помощью второго преобразователя (30) сигма-дельта, который выдает на выходе сигнал перемножения (uz = p(t)).

12. Способ по любому из пп.9-11, отличающийся тем, что первый аналоговый сигнал является измеряемым напряжением (u(t)), в частности, напряжением бытовой сети, а второй аналоговый сигнал является измеряемым током (i(t)) указанной сети в случае определения в качестве сигнала произведения (uz) мгновенного значения потребляемой из сети мощности (p(t)).

13. Способ по любому из пп.9-12, отличающийся тем, что аналоговые сигналы являются аналоговыми сигналами переменного тока.

Текст

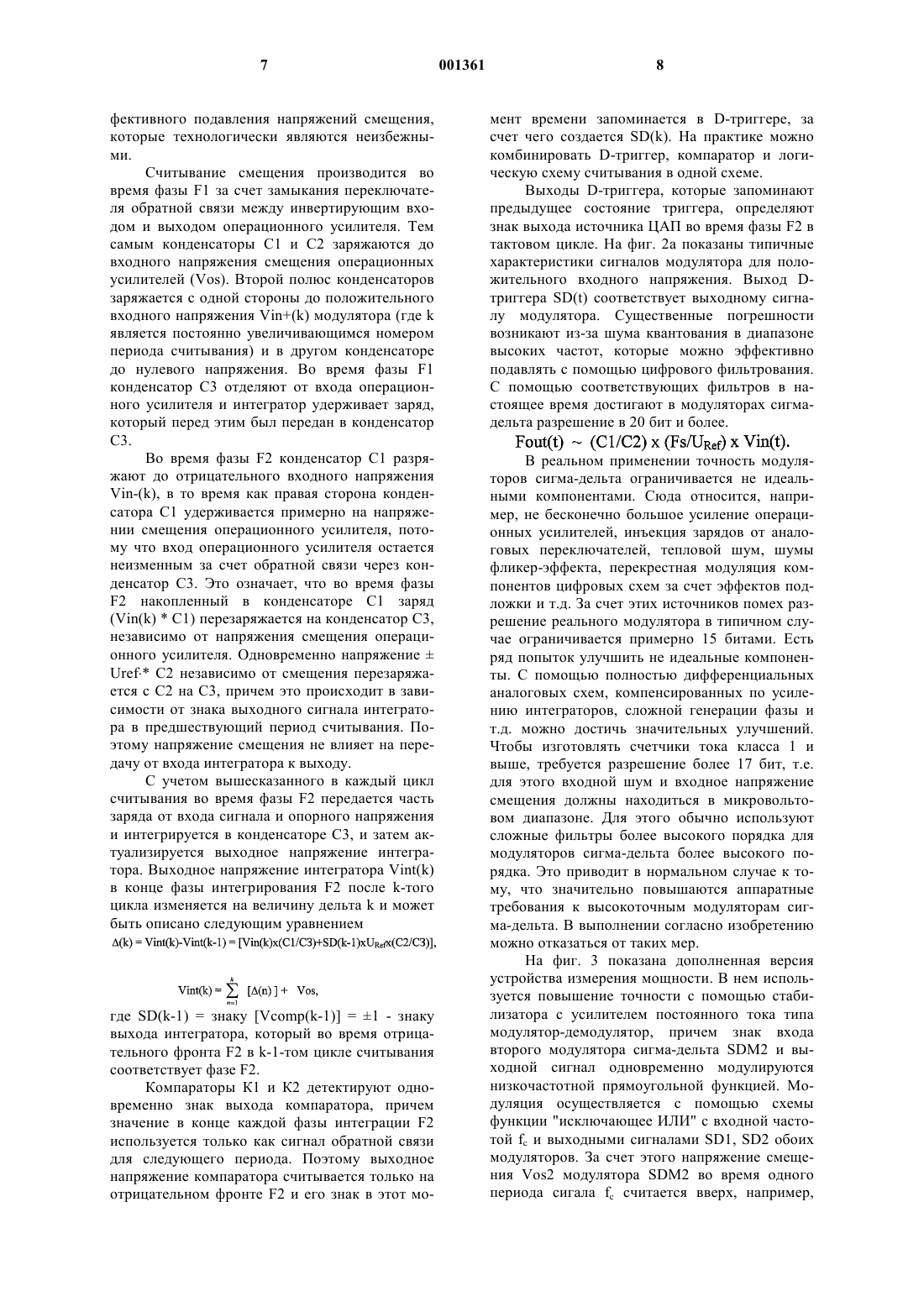

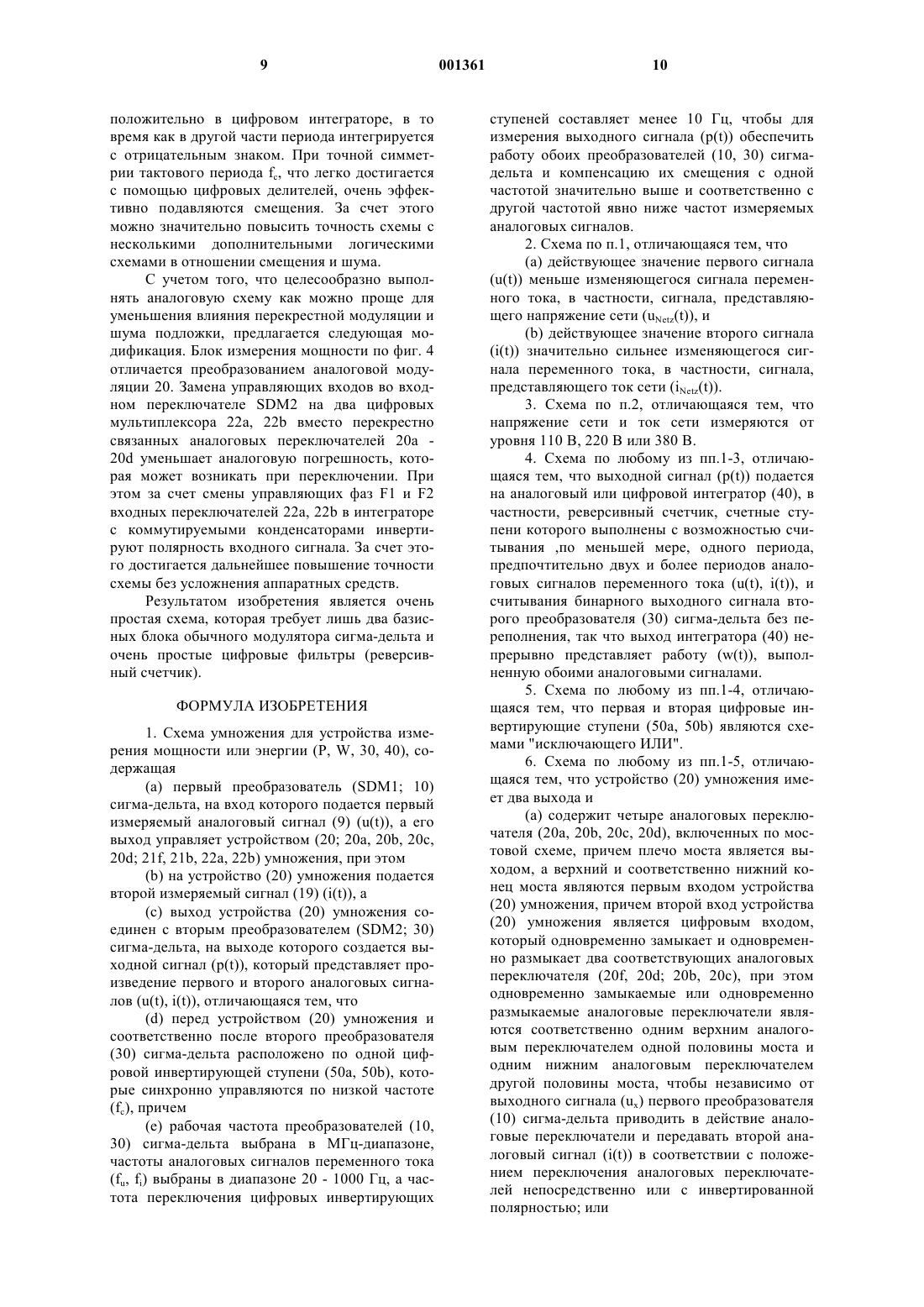

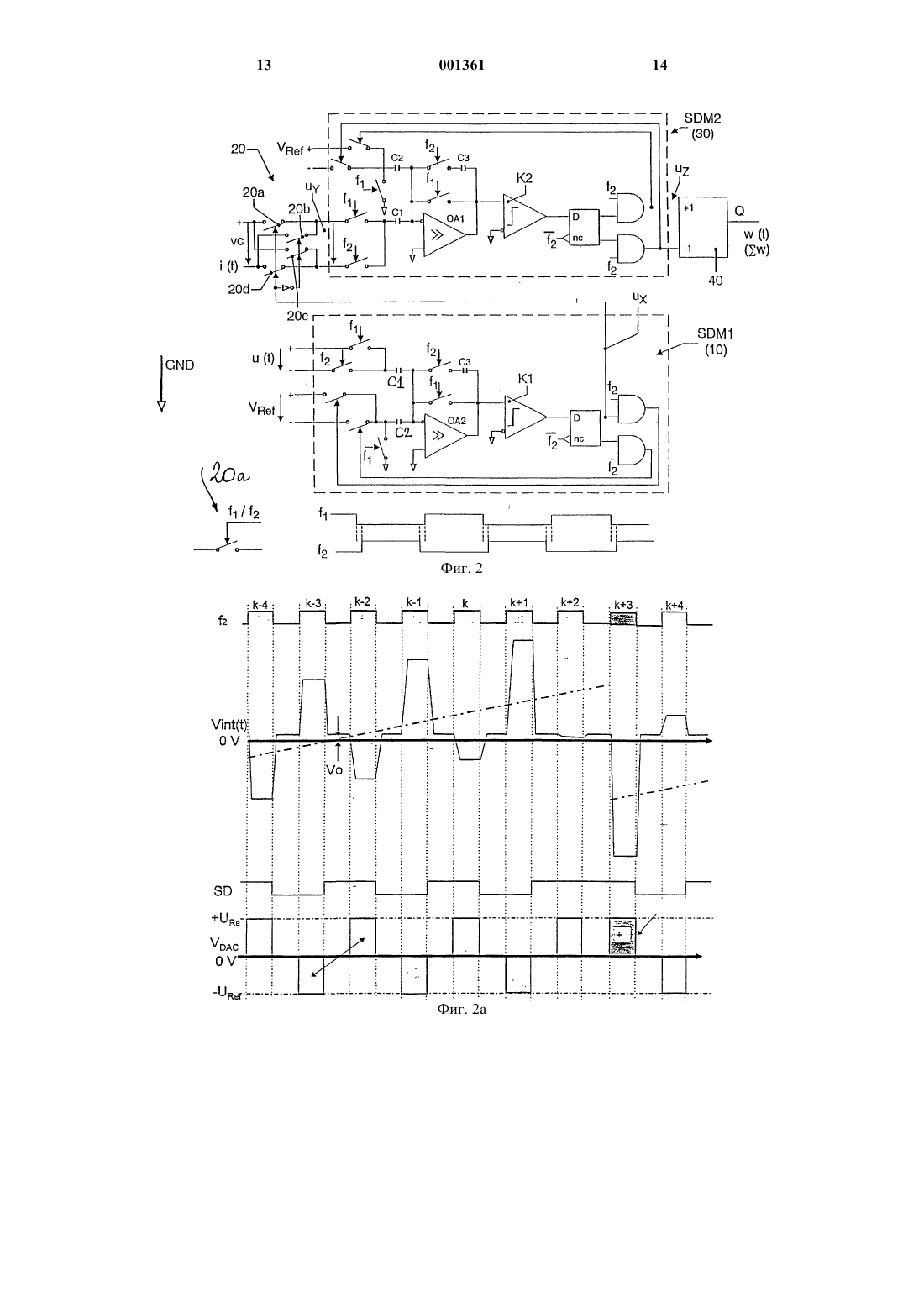

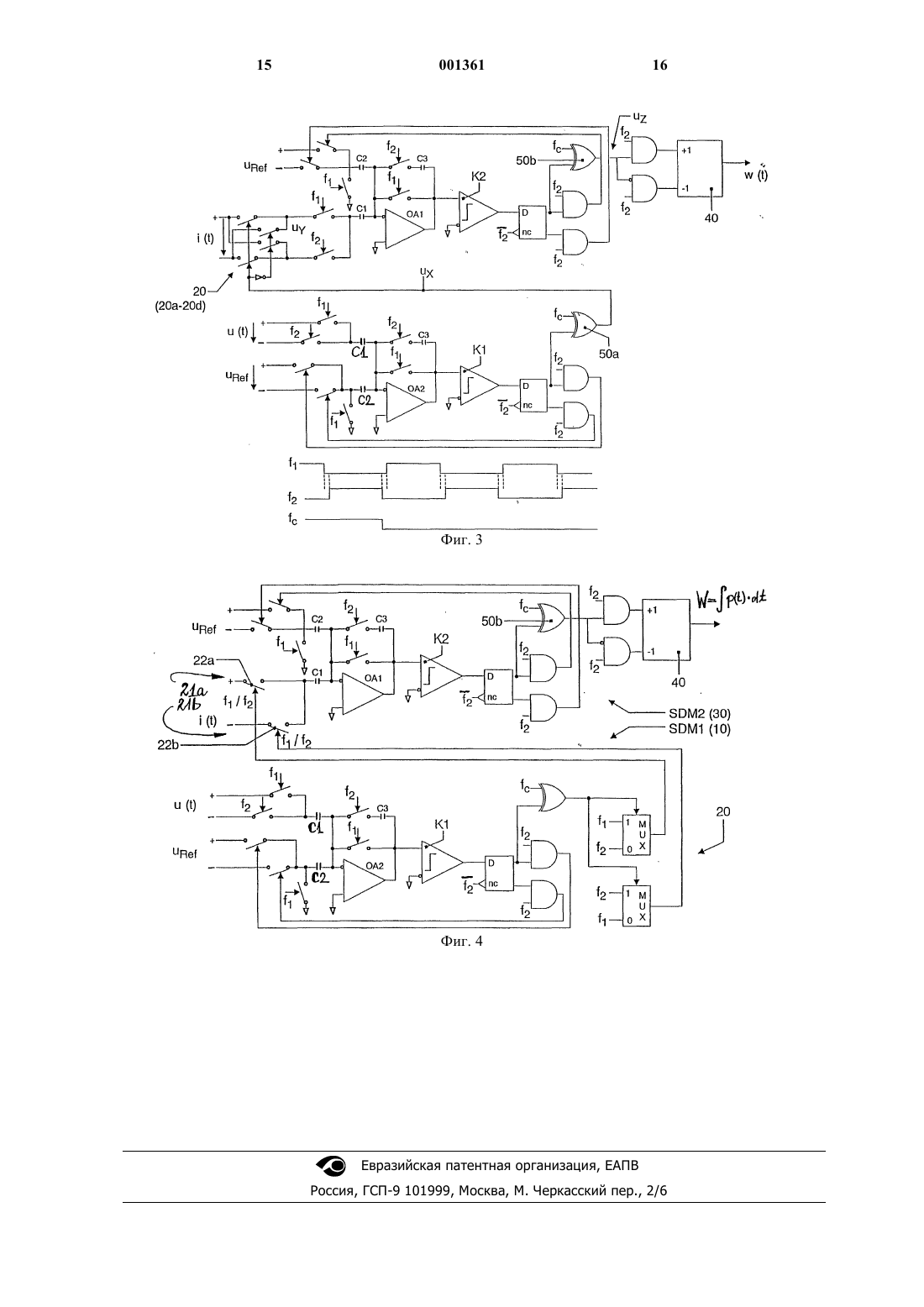

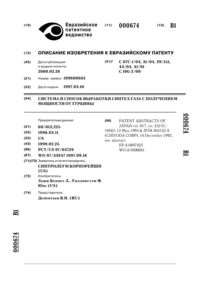

1 Изобретение относится к технике измерения мощности, с помощью которой вычисляют мгновенное значение фактически забираемой из сети мощности, при этом ток и напряжение сети являются изменяющимися величинами, напряжение в меньшей степени, однако, ощутимо, а ток - более заметно, так как его действующее значение в значительной мере определяет мощность, а именно, либо ток отбирается с определенной величиной (имеет место отбираемая мощность) или ток почти равен нулю (мощность не отбирается). Преобразователи сигма-дельта описаны в ЕР 90313050.8, они описаны там в связи с устройством измерения мощности, однако, в этом уровне техники используют аналого-цифровой преобразователь (ADU) (обозначенный там позицией 5), который неблагоприятно сказывается на стоимости изготавливаемого в большом количестве прибора. Задачей изобретения является снижение стоимости такого прибора при сохранении точности или даже повышении ее. Задача решается с помощью схемы умножения для устройства измерения мощности или энергии. При этом используют выход преобразователя сигма-дельта (или модулятора) с его током в битах для переключения знака полярности второго аналогового сигнала пропорционально плотности тока в битах выходного сигнала первого модулятора (SDM). Переключение знака осуществляет "устройство умножения", которое, однако, не является аналоговым умножителем в обычном схемотехническом смысле, а может быть выполнено в виде альтернативных решений (а) и (b) согласно п.6 формулы изобретения. При этом с помощью изобретения достигается то, что можно обойтись без аналогового умножителя для аналоговых измерительных сигналов тока и напряжения, без аналогоцифрового преобразователя с параллельным выходом и, как следствие, названного последним также без цифрового умножителя, если необходимо измерить мгновенное значение мощности. В способе согласно п.10 формулы изобретения работают с первым током в битах высокой частоты, который является цифровым током в битах. Этот ток в битах модулирует (второй) аналоговый сигнал и создает тем самым базисный сигнал uy, на который влияет первый аналоговый сигнал, а также второй сигнал и, таким образом, выполняется предпосылка определения из него сигнала перемножения uz. Если выбрать первый аналоговый сигнал, который определяет плотность тока в битах модулятора сигма-дельта, пропорциональным напряжению,а второй аналоговый сигнал выбрать пропорциональным току, то в сигнале перемножения образуется мощность, которая проявляется при оценке низкочастотной части базисного сигнала 2 с переключаемой с высокой частотой полярностью. Упомянутое выше "умножение", которое в обычных приборах измерения мощности присутствует в виде аналогового перемножителя,ограничивается при указанных выше принципах тем, что является изменением знака или умножением на 1, что можно достичь с помощью простой схемной техники с низкими затратами. Также можно отказаться от сложного цифрового умножителя, который хотя и можно создать без проблем смещения, присущих аналоговым умножителям, однако, связан со значительными схемными затратами и для достижения еще достаточной точности требует множества двоичных разрядов. Таким образом, входная величина второго преобразователя сигма-дельта соответствует мгновенной мощности, она преобразуется с помощью модулятора в цифровую плоскость и может быть с помощью реверсивного счетчика преобразована в отбираемую энергию (кВт/ч,так называемая "работа"). Интегратор может быть выполнен аналоговым или цифровым (п.4 формулы изобретения), предпочтительным является упомянутый реверсивный счетчик. Важно отметить, что предложения согласно изобретению можно использовать не только для аналоговых сигналов переменного напряжения (напряжения сети, тока сети), но также для таких "переменных напряжений", которые имеют очень низкую частоту, даже до нулевой частоты. Тем самым схема пригодна также для перемножения друг с другом сигналов постоянного напряжения без использования аналогового умножителя или аналого-цифрового преобразователя, который, исходя из блока запоминания выборки, предоставляет величину считывания заложенного в блоке запоминания выборки аналогового значения. Как раз указанные последними блоки являются дорогими и сложными и от них можно отказаться в решении согласно изобретению. Перемножение знака можно достичь простым способом с помощью мостовой схемы из четырех аналоговых переключателей (п.6 формулы изобретения, первая альтернатива), при этом аналоговые переключатели отпираются и запираются перекрестно, так что подводимый аналоговый сигнал пропускается через очень низкоомное прямое сопротивление первой пары аналоговых переключателей, или же происходит замена входных проводников и сигнал передается инвертированным через другую пару низкоомных аналоговых переключателей как сигнал, умноженный на - 1. Проблемы смещения и нелинейности аналоговых переключателей можно решить схемно-техническими способами и они не могут отрицательно воздействовать на схему согласно изобретению. 3 С помощью схемы согласно изобретению можно достичь высокого класса точности приборов измерения мощности. Можно также дополнительно создать схему подавления смещения по типу усилителя постоянного тока с модуляцией и демодуляцией сигнала, если разместить две инвертирующих ступени на цифровом уровне перед устройством инвертирования знака и после второго модулятора сигма-дельта и включить их синхронно инвертирующими или не инвертирующими(пп.5 и 9 формулы изобретения). Изобретение поясняется и дополняется ниже на нескольких примерах выполнения с помощью чертежей, на которых изображены фиг. 1 - блок-схема умножителя напряжения и тока применительно к умножителю переменного напряжения. Входные сигналы a' (t) и b'(t) могут быть также сигналами постоянного тока (переменное напряжение с частотой ноль); фиг. 2 - детальная схема по фиг.1, в нижней части которой показан аналоговый переключатель (слева) и не накладывающийся друг на друга такт для аналогового переключателя(справа), в примере переключателя 20 а; фиг. 2 а - вид сигналов модуляции, измеренных в фиг. 1; фиг. 3 - схема с цифровой коррекцией смещения с помощью двух схем 50 а, 50b функции "исключающее ИЛИ" и частоты fc 6 Гц. Такты f1, f2 для логики схем с коммутируемыми конденсаторами и частота коррекции fc показаны внизу; фиг. 4 - альтернативный вариант выполнения "умножителя" 20, который выполняет изменение знака, управляемое с помощью сигнала плотности тока в битах uх, первого преобразователя 10 сигма-дельта, причем альтернативный вариант выполнен с двумя мультиплексорами 21 а, 21b, которые управляются обеими частотами f1, f2 (в МГц диапазоне), которые управляют также схемой по фиг. 1 как схемой с коммутируемыми конденсаторами. Можно использовать единую концепцию схемы. Схема измерения мощности согласно фиг. 1 состоит из двух модуляторов 10, 30 сигмадельта, аналогового модулятора AM, тактового генератора и аккумулятора импульсов, которые соединены согласно фиг. 1. Аналоговый входной сигнал u(t), который пропорционален измеряемому напряжению, преобразуют с помощью первого модулятора 10 в цифровой ток ux(t) в битах. Снабженный одним аналоговым входом модулятор (AM) управляется двумя сигналами. С аналоговой стороны это - пропорциональный току i(t) сигнал и на цифровой управляющей стороне - сигнал ux(t) тока в битах. Модулятор умножает знак ux(t) с аналоговым входным сигналом. Таким образом, выходной сигнал модулятора в своем среднем значении пропорционален произведению i(t) и u(t), так как ux(t) в своем среднем значении соответствует u(t). Затем вы 001361 4 ходной сигнал модулятора подается на второй модулятор 30 сигма-дельта. Таким образом, выходной импульсный ток в своей оценке пропорционален также произведению i(t) и u(t). Результирующий импульсный ток uz(t) на выходе второго модулятора сигма-дельта подводится к аккумулирующему входу сумматора 40 (например, реверсивного счетчика). Выходной сигнал аккумулятора представляет собой низкочастотный ток в битах, который соответствует средней мощности. Посредством интеграции в значительной мере подавляются высокочастотные шумы квантования модуляторов. Оба идентичных блока схемы состоят из синхронных модуляторов сигма-дельта первого порядка. Дополнительно к обоим модуляторам сигма-дельта почти не требуется других схемных элементов. Как раз это является преимуществом. Обычный модулятор сигма-дельта первого порядка содержит интегратор, 1-битовый квантизатор (компаратор), один выход, который считывается с частотой считывания Fs, и 1 битовый цифроаналоговый преобразователь,который выдает +/- Uref в соответствии со знаком считанного сигнала компаратора. В каждой точке считывания интегратор интегрирует разницу (сигнал ошибки) между входом u(t) и выходом преобразователя. Знак разницы в течение периода считывания запоминается в квантизаторе. Если выход компаратора y(t) является логической 1, то положительное напряжение+Uref подается обратно на вход интегратора. Подаваемый обратно сигнал в своей последовательности импульсов пропорционален входному сигналу, так как ошибка интегратора отрегулирована на ноль. В качестве Z-трансформированного сигнала функцию модулятора можно описать следующей формулой:y(z) = x(z) + (1-z-1) x Q(z),где Q(z) является шумом квантования модулятора. Спектр второго члена уравнения находится в высокочастотном диапазоне немного ниже под базисным диапазоном и может быть поэтому легко подавлен с помощью цифрового фильтрования, а также, например, с помощью интегрирования. Большим преимуществом модуляторов сигма-дельта является их хорошая интегрируемость в обычные технологии интегральных схем. Типичные модуляторы сигма-дельта используют обычные интегральные схемы с интеграторами с коммутируемыми конденсаторами. Это представляет одну из самых эффективных технологий микроэлектроники, поскольку схемы с коммутируемыми конденсаторами можно легко изготовлять с высоким качеством с помощью технологии массового производства, как,например, КМОП. Принцип действия схем с коммутируемыми конденсаторами использует перенос зарядов между конденсаторами, коммутируемыми с по 5 мощью аналоговых переключателей. При этом частоту коммутации выбирают так, что она значительно выше частоты входных сигналов. В примере счетчика тока частота считывания находится в типичном случае в диапазоне МГц по сравнению с частотой 50 или 60 Гц входных сигналов. Аналоговый переключатель в схемах с коммутируемыми конденсаторами управляется с помощью не накладывающихся друг на друга прямоугольных сигналов с противоположной фазой (см., например, фиг. 2 внизу). Тактовый генератор схемы строят так, что переключающие фронты сигналов не накладываются друг на друга с достаточным запасом. Это предотвращает потери заряда при передаче. Во время одной фазы тактового сигнала одна часть конденсаторов подключается к источнику напряжения и заряжается до этого напряжения. Во время второй фазы тактового сигнала заряды с помощью аналоговых переключателей и операционных усилителей переносятся на другие конденсаторы. В результате выходной сигнал можно описать с помощью математической операции с входным сигналом, как, например,сложение, вычитание, умножение с неизменными коэффициентами, задержка или интеграция,для чего необходимы только конденсаторы с различными соотношениями, аналоговые переключатели и операционные усилители. Например, высокоомное сопротивление можно аппроксимировать с помощью небольшого конденсатоpa Cs, который переключается с частотой переключения Fs. Эквивалентное сопротивление соответствует l/(FsCs). Если этот сигнал соединяют с не переключаемым конденсаторомCint или с суммирующим узлом операционного усилителя с не переключаемым конденсатором в цепи обратной связи, то с помощью этого "сопротивления" можно установить постоянную времени RC = [(Cint/(CsFs)], которая определяется только соотношением конденсаторов и частотой переключения. Это является большим преимуществом схем с коммутируемыми конденсаторами, так как с помощью обычных технологий изготовления интегральных схем как раз соотношение конденсаторов можно получать очень точным, в то время как абсолютные значения конденсаторов с помощью обычных технологий изготовления интегральных схем можно выполнять только не точно. Это является причиной того, что техника схем с коммутируемыми конденсаторами используется во многих принципах преобразования с большой степенью разрешения. На фиг. 2 показано возможное выполнение схемы согласно изобретению. В типичных случаях такие схемы выполняют полностью дифференциальными в аналоговой ветви данных. Для упрощения изображения здесь показана только несимметричная схема с коммутируемыми конденсаторами. Аналоговый модулятор 6 представлен четырьмя включенными перекрестно аналоговыми переключателями 20a - 20d,которые позволяют инвертировать полярность входного сигнала i(t). Входной сигнал первого модулятора сигма-дельта SDM1 выдает выходной сигнал ux(t). Если сигнал равен логическому нулю, то выход модулятора uy(t) = -i(t). Еслиux(t) = -1, то выходной сигнал модулятора соответствует входному сигналу uy(t) = i(t). Схемы отдельных модуляторов сигма-дельта изображены внутри штриховых рамок. МодуляторыSDM1 и SDM2 используют известную технику схем с коммутируемыми конденсаторами с автоматическим нулем с двумя дифференциальными входами и состоят из операционных усилителей ОА 2 и ОА 1, входного коммутируемого конденсатора С 1, опорного коммутируемого конденсатора С 2, интегрирующего конденсатора С 3 и различных переключателей, которые управляются двумя не накладывающимися друг на друга тактовыми сигналами f1 и f2. Знак интегрированного дифференциального сигнала между входом модулятора и выходом ЦАП во время одного периода переключения определяется компаратором К 1 или К 2 и запоминается на один период тактовых импульсов в D-триггере. Выход компаратора, состоящий из двух схем И,управляет через ЦАП источником опорных напряжений (+Vref или -Vref), которые интегрируются в следующем периоде считывания. Дополнительно с помощью схем И модулятораSDM2 30 выходные импульсные токи разделяются так, что один представляет мгновенную положительную измеряемую мощность uz(t) и второй выход представляет отрицательную измеряемую мощность. Два импульсных тока аккумулируются в n-битовом реверсивном счетчике. Выход счетчика выдает импульсный токw(t) с плотностью импульсов, которая соответствует среднему значению активной мощности. Вход модулятора сигма-дельта (например, u(t) или uy(t переключается на дифференциальные входные сигналы интегратора. Опорный вход интегратора переключается с выходом ЦАП(+Vref или -Vref) с помощью общего переключателя, который соединяет интегратор и ЦАП. Интегратор с коммутируемыми конденсаторами содержит самостоятельную настройку на ноль(автоматическая установка нуля), которая сокращает напряжение смещения операционных усилителей и низкочастотный шум. Это достигается с помощью коррелированного двойного считывания. При коррелированном двойном считывании каждый период считывания разделяется на две подгруппы. Во время первой подгруппы считывается смещение и во время второй подгруппы смещение вычитается из входного сигнала. За счет этого можно достичь эф 7 фективного подавления напряжений смещения,которые технологически являются неизбежными. Считывание смещения производится во время фазы F1 за счет замыкания переключателя обратной связи между инвертирующим входом и выходом операционного усилителя. Тем самым конденсаторы С 1 и С 2 заряжаются до входного напряжения смещения операционных усилителей (Vos). Второй полюс конденсаторов заряжается с одной стороны до положительного входного напряжения Vin+(k) модулятора (где k является постоянно увеличивающимся номером периода считывания) и в другом конденсаторе до нулевого напряжения. Во время фазы F1 конденсатор С 3 отделяют от входа операционного усилителя и интегратор удерживает заряд,который перед этим был передан в конденсатор С 3. Во время фазы F2 конденсатор С 1 разряжают до отрицательного входного напряженияVin-(k), в то время как правая сторона конденсатора С 1 удерживается примерно на напряжении смещения операционного усилителя, потому что вход операционного усилителя остается неизменным за счет обратной связи через конденсатор С 3. Это означает, что во время фазы(Vin(k)С 1) перезаряжается на конденсатор С 3,независимо от напряжения смещения операционного усилителя. Одновременно напряжениеUref С 2 независимо от смещения перезаряжается с С 2 на С 3, причем это происходит в зависимости от знака выходного сигнала интегратора в предшествующий период считывания. Поэтому напряжение смещения не влияет на передачу от входа интегратора к выходу. С учетом вышесказанного в каждый цикл считывания во время фазы F2 передается часть заряда от входа сигнала и опорного напряжения и интегрируется в конденсаторе С 3, и затем актуализируется выходное напряжение интегратора. Выходное напряжение интегратора Vint(k) в конце фазы интегрирования F2 после k-того цикла изменяется на величину дельта k и может быть описано следующим уравнением где SD(k-1) = знаку [Vcomp(k-1)] = 1 - знаку выхода интегратора, который во время отрицательного фронта F2 в k-1-том цикле считывания соответствует фазе F2. Компараторы К 1 и К 2 детектируют одновременно знак выхода компаратора, причем значение в конце каждой фазы интеграции F2 используется только как сигнал обратной связи для следующего периода. Поэтому выходное напряжение компаратора считывается только на отрицательном фронте F2 и его знак в этот мо 001361 8 мент времени запоминается в D-триггере, за счет чего создается SD(k). На практике можно комбинировать D-триггер, компаратор и логическую схему считывания в одной схеме. Выходы D-триггера, которые запоминают предыдущее состояние триггера, определяют знак выхода источника ЦАП во время фазы F2 в тактовом цикле. На фиг. 2 а показаны типичные характеристики сигналов модулятора для положительного входного напряжения. Выход Dтриггера SD(t) соответствует выходному сигналу модулятора. Существенные погрешности возникают из-за шума квантования в диапазоне высоких частот, которые можно эффективно подавлять с помощью цифрового фильтрования. С помощью соответствующих фильтров в настоящее время достигают в модуляторах сигмадельта разрешение в 20 бит и более. В реальном применении точность модуляторов сигма-дельта ограничивается не идеальными компонентами. Сюда относится, например, не бесконечно большое усиление операционных усилителей, инъекция зарядов от аналоговых переключателей, тепловой шум, шумы фликер-эффекта, перекрестная модуляция компонентов цифровых схем за счет эффектов подложки и т.д. За счет этих источников помех разрешение реального модулятора в типичном случае ограничивается примерно 15 битами. Есть ряд попыток улучшить не идеальные компоненты. С помощью полностью дифференциальных аналоговых схем, компенсированных по усилению интеграторов, сложной генерации фазы и т.д. можно достичь значительных улучшений. Чтобы изготовлять счетчики тока класса 1 и выше, требуется разрешение более 17 бит, т.е. для этого входной шум и входное напряжение смещения должны находиться в микровольтовом диапазоне. Для этого обычно используют сложные фильтры более высокого порядка для модуляторов сигма-дельта более высокого порядка. Это приводит в нормальном случае к тому, что значительно повышаются аппаратные требования к высокоточным модуляторам сигма-дельта. В выполнении согласно изобретению можно отказаться от таких мер. На фиг. 3 показана дополненная версия устройства измерения мощности. В нем используется повышение точности с помощью стабилизатора с усилителем постоянного тока типа модулятор-демодулятор, причем знак входа второго модулятора сигма-дельта SDM2 и выходной сигнал одновременно модулируются низкочастотной прямоугольной функцией. Модуляция осуществляется с помощью схемы функции "исключающее ИЛИ" с входной частотой fс и выходными сигналами SD1, SD2 обоих модуляторов. За счет этого напряжение смещения Vos2 модулятора SDM2 во время одного периода сигала fс считается вверх, например, 9 положительно в цифровом интеграторе, в то время как в другой части периода интегрируется с отрицательным знаком. При точной симметрии тактового периода fс, что легко достигается с помощью цифровых делителей, очень эффективно подавляются смещения. За счет этого можно значительно повысить точность схемы с несколькими дополнительными логическими схемами в отношении смещения и шума. С учетом того, что целесообразно выполнять аналоговую схему как можно проще для уменьшения влияния перекрестной модуляции и шума подложки, предлагается следующая модификация. Блок измерения мощности по фиг. 4 отличается преобразованием аналоговой модуляции 20. Замена управляющих входов во входном переключателе SDM2 на два цифровых мультиплексора 22 а, 22b вместо перекрестно связанных аналоговых переключателей 20 а 20d уменьшает аналоговую погрешность, которая может возникать при переключении. При этом за счет смены управляющих фаз F1 и F2 входных переключателей 22a, 22b в интеграторе с коммутируемыми конденсаторами инвертируют полярность входного сигнала. За счет этого достигается дальнейшее повышение точности схемы без усложнения аппаратных средств. Результатом изобретения является очень простая схема, которая требует лишь два базисных блока обычного модулятора сигма-дельта и очень простые цифровые фильтры (реверсивный счетчик). ФОРМУЛА ИЗОБРЕТЕНИЯ 1. Схема умножения для устройства измерения мощности или энергии (Р, W, 30, 40), содержащая(a) первый преобразователь (SDM1; 10) сигма-дельта, на вход которого подается первый измеряемый аналоговый сигнал (9) (u(t, а его выход управляет устройством (20; 20 а, 20b, 20 с,20d; 21f, 21b, 22 а, 22b) умножения, при этом(b) на устройство (20) умножения подается второй измеряемый сигнал (19) (i(t, a(c) выход устройства (20) умножения соединен с вторым преобразователем (SDM2; 30) сигма-дельта, на выходе которого создается выходной сигнал (p(t, который представляет произведение первого и второго аналоговых сигналов (u(t), i(t, отличающаяся тем, что(d) перед устройством (20) умножения и соответственно после второго преобразователя(30) сигма-дельта расположено по одной цифровой инвертирующей ступени (50 а, 50b), которые синхронно управляются по низкой частоте(e) рабочая частота преобразователей (10,30) сигма-дельта выбрана в МГц-диапазоне,частоты аналоговых сигналов переменного тока(fu, fi) выбраны в диапазоне 20 - 1000 Гц, а частота переключения цифровых инвертирующих 10 ступеней составляет менее 10 Гц, чтобы для измерения выходного сигнала (p(t обеспечить работу обоих преобразователей (10, 30) сигмадельта и компенсацию их смещения с одной частотой значительно выше и соответственно с другой частотой явно ниже частот измеряемых аналоговых сигналов. 2. Схема по п.1, отличающаяся тем, что(a) действующее значение первого сигнала(u(t меньше изменяющегося сигнала переменного тока, в частности, сигнала, представляющего напряжение сети (uNetz(t, и(b) действующее значение второго сигнала(i(t значительно сильнее изменяющегося сигнала переменного тока, в частности, сигнала,представляющего ток сети (iNetz(t. 3. Схема по п.2, отличающаяся тем, что напряжение сети и ток сети измеряются от уровня 110 В, 220 В или 380 В. 4. Схема по любому из пп.1-3, отличающаяся тем, что выходной сигнал (p(t подается на аналоговый или цифровой интегратор (40), в частности, реверсивный счетчик, счетные ступени которого выполнены с возможностью считывания ,по меньшей мере, одного периода,предпочтительно двух и более периодов аналоговых сигналов переменного тока (u(t), i(t, и считывания бинарного выходного сигнала второго преобразователя (30) сигма-дельта без переполнения, так что выход интегратора (40) непрерывно представляет работу (w(t, выполненную обоими аналоговыми сигналами. 5. Схема по любому из пп.1-4, отличающаяся тем, что первая и вторая цифровые инвертирующие ступени (50 а, 50b) являются схемами "исключающего ИЛИ". 6. Схема по любому из пп.1-5, отличающаяся тем, что устройство (20) умножения имеет два выхода и(а) содержит четыре аналоговых переключателя (20 а, 20b, 20 с, 20d), включенных по мостовой схеме, причем плечо моста является выходом, а верхний и соответственно нижний конец моста являются первым входом устройства(20) умножения, причем второй вход устройства(20) умножения является цифровым входом,который одновременно замыкает и одновременно размыкает два соответствующих аналоговых переключателя (20f, 20d; 20b, 20 с), при этом одновременно замыкаемые или одновременно размыкаемые аналоговые переключатели являются соответственно одним верхним аналоговым переключателем одной половины моста и одним нижним аналоговым переключателем другой половины моста, чтобы независимо от выходного сигнала (ux) первого преобразователя(10) сигма-дельта приводить в действие аналоговые переключатели и передавать второй аналоговый сигнал (i(t в соответствии с положением переключения аналоговых переключателей непосредственно или с инвертированной полярностью; или 12 ческих уровней пропорционально первому аналоговому сигналу (u(t, частота которого значительно ниже частоты тока в битах;(b) первых цифровой ток в битах (ux) переключает знак или полярность (20) второго аналогового сигнала (i(t, частота которого (fi) по порядку величины совпадает с частотой первого аналогового сигнала, для получения базисного сигнала с переключаемой с высокой частотой полярностью (uy), который пригоден для определения сигнала перемножения (uz), отличающийся тем, что(c) рабочие частоты (f1, f2) управления плотностью и переключения (10, 20) в основном больше частот (fu, fi) аналоговых сигналов на фактор 105 - 106, однако, если используют аналоговые сигналы постоянного тока, то рабочие частоты (f1, f2) выше 1 МГц. 10. Способ по п.9, отличающийся тем, что устройство (20) умножения является устройством инвертирования знака. 11. Способ по п.9 или 10, отличающийся тем, что базисный сигнал (uy) без аналогоцифрового преобразования с помощью параллельного выхода или образования произведения в отношении его низкочастотной составляющей оценивают, в частности, с помощью второго преобразователя (30) сигма-дельта, который выдает на выходе сигнал перемножения (uz =p(t. 12. Способ по любому из пп.9-11, отличающийся тем, что первый аналоговый сигнал является измеряемым напряжением (u(t, в частности, напряжением бытовой сети, а второй аналоговый сигнал является измеряемым током(i(t указанной сети в случае определения в качестве сигнала произведения (uz) мгновенного значения потребляемой из сети мощности (p(t. 13. Способ по любому из пп.9-12, отличающийся тем, что аналоговые сигналы являются аналоговыми сигналами переменного тока.(b) имеет два мультиплексора, мультиплексные входы которых соединены вместе и образуют второй вход устройства (20) умножения, на который подводится выходной сигнал первого преобразователя (10) сигма-дельта, при этом первый вход (21 а, 21b) устройства (20) умножения имеет два аналоговых переключателя (22 а, 22b), которые в зависимости от выходных сигналов мультиплексоров пропускают или второй аналоговый сигнал (i(t, или аналоговоинвертированный второй налоговый сигнал(-i(t в качестве выходного сигнала устройства(20) умножения, причем к обоим мультиплексорам на их входы перемножения постоянно подводятся противоположные частотные сигналы(f1, f2; f2, f1), которые являются не накладывающимися друг на друга тактовыми сигналами для управления аналоговыми переключателями преобразователей (10, 30) сигма-дельта, выполненных по схеме с коммутируемыми конденсаторами. 7. Схема по любому из пп.1-6, отличающаяся тем, что преобразователи (30, 10) сигмадельта, в качестве модуляторов сигма-дельта первого порядка выдают на выходе пропорциональную аналоговому входному сигналу (u(t),i(t плотность тока в битах, в которой отношение уровня логической единицы к уровню логического нуля пропорционально мгновенному значению входного сигнала. 8. Схема по п.5, отличающаяся тем, что частота переключении низкой частоты (fс) значительно ниже частоты (fu, fi) аналоговых сигналов переменного тока (u(t), i(t, если сигналы переменного тока используются в качестве входных сигналов. 9. Способ измерения мгновенного значения мощности (p(t в устройстве измерения, в частности, для напряжения сети и тока сети, при котором(a) управляют цифровым током в битах высокой частоты (ux) по плотности обоих логи Фиг. 1

МПК / Метки

МПК: G01R 21/133

Метки: мгновенного, мощности, способ, умножения, схема, устройства, значения, измерения

Код ссылки

<a href="https://eas.patents.su/9-1361-shema-umnozheniya-dlya-ustrojjstva-izmereniya-moshhnosti-i-sposob-izmereniya-mgnovennogo-znacheniya-moshhnosti.html" rel="bookmark" title="База патентов Евразийского Союза">Схема умножения для устройства измерения мощности и способ измерения мгновенного значения мощности</a>