Демультиплексор и способ демультиплексирования

Номер патента: 22652

Опубликовано: 29.02.2016

Авторы: Ямамото Макико, Окада Сатоси, Икегая Рьёдзи, Ёкокава Такаси

Формула / Реферат

1. Демультиплексор, содержащий

запоминающее устройство, имеющее емкость накопителя, требуемую для сохранения mb битов в направлении строки и сохранения N/(mb) битов в направлении столбцов, и выполненное с возможностью записи кодовых битов для кода LDPC (код с малой плотностью проверки на четность), имеющего длину кода N битов, подаваемых в него, в направлении столбцов для сохранения кодовых битов в направлении строки и в направлении столбца и считывания m битов кодовых битов LDPC в направлении строки, при этом m битов кодовых битов для кода LDPC установлены как один символ и b представляет собой заданное положительное целое число; и

средство замены, соединенное с запоминающим устройством и выполненное с возможностью замены mb кодовых битов таким образом, что кодовые биты после замены формируют биты символов, представляющие символы, в случае, когда mb кодовых битов, считанных в направлении строки упомянутого средства сохранения, установлены как b символов,

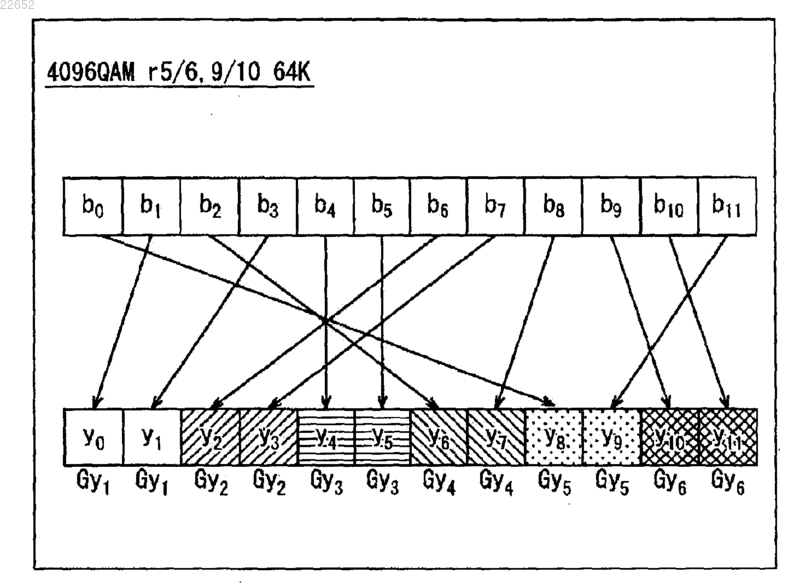

в котором код LDPC представляет собой код LDPC, предписанный в соответствии со стандартом DVB-S.2 или DVB-T.2, который имеет длину N кода 64800 битов и имеет скорость кодирования 5/6 или 9/10;

m битов представляют собой 12, в то время как целое число b равно 1;

12 битов из кодовых битов отображают как один символ на некоторые из 4096 точек сигнала, предписанных в соответствии с 4096QAM (квадратурная амплитудная модуляция); и

упомянутое запоминающее устройство имеет 12 столбцов для сохранения 12´1 битов в направлении строки и сохранения 64800/(12´1) битов в направлении столбцов;

упомянутое средство замены выполнено с возможностью замены для назначения

бита b0 для бита у8,

бита b1 для бита у0,

бита b2 для бита y6,

бита b3 для бита у1,

бита b4 для бита y4,

бита b5 для бита y5,

бита b6 для бита y2,

бита b7 для бита у3,

бита b8 для бита у7,

бита b9 для бита у10,

бита b10 для бита у11,

бита b11 для бита y9

как для кода LDPC со скоростью кодирования 5/6, так и для кода LDPC со скоростью кодирования 9/10, когда i+1-й бит от старшего значащего бита 12´1 кодовых битов, считываемых в направлении строки упомянутого средства сохранения, представлен как бит bi и i+1-й бит от старшего значащего бита 12´1 битов символов одного символа представлен как бит yi.

2. Демультиплексор, содержащий

запоминающее устройство, имеющее емкость накопителя, требуемую для сохранения mb битов в направлении строки и сохранения N/(mb) битов в направлении столбцов, и выполненное с возможностью записи кодовых битов для кода LDPC (код с малой плотностью проверки на четность), имеющего длину кода N битов, подаваемых в него, в направлении столбцов для сохранения кодовых битов в направлении строки и в направлении столбца и считывания m битов кодовых битов LDPC в направлении строки, при этом m битов кодовых битов для кода LDPC установлены как один символ и b представляет собой заданное положительное целое число; и

средство замены, соединенное с запоминающим устройством и выполненное с возможностью замены mb кодовых битов таким образом, что кодовые биты после замены формируют биты символов, представляющие символы, в случае, когда mb кодовых битов, считанных в направлении строки упомянутого средства сохранения, установлены как b символов,

в котором код LDPC представляет собой код LDPC, предписанный в соответствии со стандартом DVB-S.2 или DVB-T.2, который имеет длину N кода 64800 битов и скорость кодирования 9/10;

m битов представляют собой 12, в то время как целое число b равно 1;

12 битов из кодовых битов отображают как один символ на некоторые из 4096 точек сигнала, предписанных в соответствии с 4096QAM (квадратурная амплитудная модуляция); и

упомянутое запоминающее устройство имеет 12 столбцов для сохранения 12´1 битов в направлении строки и сохранения 64800/(12´1) битов в направлении столбцов;

упомянутое средство замены выполнено с возможностью замены для назначения

бита b0 для бита у8,

бита b1 для бита у0,

бита b2 для бита у6,

бита b3 для бита у1,

бита b4 для бита y4,

бита b5 для бита у5,

бита b6 для бита у2,

бита b7 для бита у3,

бита b8 для бита у7,

бита b9 для бита у10,

бита b10 для бита у11,

бита b11 для бита у9

для кода LDPC со скоростью кодирования 9/10, когда i+1-й бит от старшего значащего бита 12´1 кодовых битов, считываемых в направлении строки упомянутого средства сохранения, представлен как бит bi и i+1-й бит от старшего значащего бита 12´1 битов символов одного символа представлен как бит yi.

3. Демультиплексор, содержащий

запоминающее устройство, имеющее емкость накопителя, требуемую для сохранения mb битов в направлении строки и сохранения N/(mb) битов в направлении столбцов, и выполненное с возможностью записи кодовых битов для кода LDPC (код с малой плотностью проверки на четность), имеющего длину кода N битов, подаваемых в него, в направлении столбцов для сохранения кодовых битов в направлении строки и в направлении столбца и считывания m битов кодовых битов LDPC в направлении строки, при этом m битов кодовых битов для кода LDPC установлены как один символ и b представляет собой заданное положительное целое число; и

средство замены, соединенное с запоминающим устройством и выполненное с возможностью замены mb кодовых битов таким образом, что кодовые биты после замены формируют биты символов, представляющие символы, в случае, когда mb кодовых битов, считанных в направлении строки упомянутого средства сохранения, установлены как b символов;

в котором код LDPC представляет собой код LDPC, предписанный в соответствии со стандартом DVB-S.2 или DVB-T.2, который имеет длину N кода 16200 битов и скорость кодирования 3/4, 5/6 или 8/9;

m битов представляют собой 10, в то время как целое число b равно 2;

10 битов из кодовых битов отображают как один символ на некоторые из 1024 точек сигнала, предписанных в соответствии с 1024QAM (квадратурная амплитудная модуляция); и

упомянутое запоминающее устройство имеет 20 столбцов для сохранения 10´2 битов в направлении строки и содержит N/(10´2) битов в направлении столбцов;

упомянутое средство замены выполнено с возможностью замены для назначения

бита b0 для бита y8,

бита b1 для бита у3,

бита b2 для бита у7,

бита b3 для бита у10,

бита b4 для бита у19,

бита b5 для бита y4,

бита b6 для бита у9,

бита b7 для бита y5,

бита b8 для бита у17,

бита b9 для бита y6,

бита b10 для бита у14,

бита b11 для бита у11,

бита b12 для бита y2,

бита b13 для бита y18,

бита b14 для бита y16,

бита b15 для бита y15,

бита b16 для бита у0,

бита b17 для бита у1,

бита b18 для бита у13,

бита b19 для бита у12

для кода LDPC с длиной N кода 16200 битов и скоростью кодирования 3/4, 5/6 или 8/9, когда i+1-й бит от старшего значащего бита 10´2 кодовых битов, считываемых в направлении строки упомянутого средства сохранения, представлен как бит bi и i+1-й бит от старшего значащего бита 10´2 битов символов одного символа представлен как бит yi.

4. Демультиплексор, содержащий

запоминающее устройство, имеющее емкость накопителя, требуемую для сохранения mb битов в направлении строки и сохранения N/(mb) битов в направлении столбцов, и выполненное с возможностью записи кодовых битов для кода LDPC (код с малой плотностью проверки на четность), имеющего длину кода N битов, подаваемых в него, в направлении столбцов для сохранения кодовых битов в направлении строки и в направлении столбца и считывания m битов кодовых битов LDPC в направлении строки, при этом m битов кодовых битов для кода LDPC установлены как один символ и b представляет собой заданное положительное целое число; и

средство замены, соединенное с запоминающим устройством и выполненное с возможностью замены mb кодовых битов таким образом, что кодовые биты после замены формируют биты символов, представляющие символы, в случае, когда mb кодовых битов, считанных в направлении строки упомянутого средства сохранения, установлены как b символов,

в котором код LDPC представляет собой код LDPC, предписанный в соответствии со стандартом DVB-S.2 или DVB-T.2, который имеет длину N кода 16200 битов и скорость кодирования 3/4;

m битов представляют собой 10, в то время как целое число b равно 2;

10 битов из кодовых битов отображают как один символ на некоторые из 1024 точек сигнала, предписанных в соответствии с 1024QAM (квадратурная амплитудная модуляция); и

упомянутое запоминающее устройство имеет 20 столбцов для сохранения 10´2 битов в направлении строки и содержит N/(10´2) битов в направлении столбцов;

упомянутое средство замены выполнено с возможностью замены для назначения

бита b0 для бита y8,

бита b1 для бита у3,

бита b2 для бита у7,

бита b3 для бита у10,

бита b4 для бита y19,

бита b5 для бита y4,

бита b6 для бита у9,

бита b7 для бита y5,

бита b8 для бита у17,

бита b9 для бита y6,

бита b10 для бита у14,

бита b11 для бита у11,

бита b12 для бита у2,

бита b13 для бита y18,

бита b14 для бита y16,

бита b15 для бита y15,

бита b16 для бита у0,

бита b17 для бита у1,

бита b18 для бита у13,

бита b19 для бита у12

для кода LDPC с длиной N кода 16200 битов и скоростью кодирования 3/4, когда i+1-й бит от старшего значащего бита 10´2 кодовых битов, считываемых в направлении строки упомянутого средства сохранения, представлен как бит bi, и i+1-й бит от старшего значащего бита 10´2 битов символов одного символа представлен как бит yi.

5. Демультиплексор, содержащий

запоминающее устройство, имеющее емкость накопителя, требуемую для сохранения mb битов в направлении строки и сохранения N/(mb) битов в направлении столбцов, и выполненное с возможностью записи кодовых битов для кода LDPC (код с малой плотностью проверки на четность), имеющего длину кода N битов, подаваемых в него, в направлении столбцов для сохранения кодовых битов в направлении строки и в направлении столбца и считывания m битов кодовых битов LDPC в направлении строки, при этом m битов кодовых битов для кода LDPC установлены как один символ и b представляет собой заданное положительное целое число; и

средство замены, соединенное с запоминающим устройством и выполненное с возможностью замены mb кодовых битов таким образом, что кодовые биты после замены формируют биты символов, представляющие символы, в случае, когда mb кодовых битов, считанных в направлении строки упомянутого средства сохранения, установлены как b символов,

в котором код LDPC представляет собой код LDPC, предписанный в соответствии со стандартом DVB-S.2 или DVB-T.2, который имеет длину N кода 16200 битов и скорость кодирования 5/6;

m битов представляют собой 10, в то время как целое число b равно 2;

10 битов из кодовых битов отображают как один символ на некоторые из 1024 точек сигнала, предписанных в соответствии с 1024QAM (квадратурная амплитудная модуляция); и

упомянутое запоминающее устройство имеет 20 столбцов для сохранения 10´2 битов в направлении строки и содержит N/(10´2) битов в направлении столбцов;

упомянутое средство замены выполнено с возможностью замены для назначения

бита b0 для бита y8,

бита b1 для бита у3,

бита b2 для бита у7,

бита b3 для бита у10,

бита b4 для бита y19,

бита b5 для бита y4,

бита b6 для бита у9,

бита b7 для бита y5,

бита b8 для бита у17,

бита b9 для бита y6,

бита b10 для бита у14,

бита b11 для бита у11,

бита b12 для бита у2,

бита b13 для бита у18,

бита b14 для бита y16,

бита b15 для бита y15,

бита b16 для бита у0,

бита b17 для бита у1,

бита b18 для бита у13,

бита b19 для бита у12

для кода LDPC с длиной N кода 16200 битов и скоростью кодирования 5/6, когда i+1-й бит от старшего значащего бита 10´2 кодовых битов, считываемых в направлении строки упомянутого средства сохранения, представлен как бит bi и i+1-й бит от старшего значащего бита 10´2 битов символов одного символа представлен как бит yi.

6. Демультиплексор, содержащий

запоминающее устройство, имеющее емкость накопителя, требуемую для сохранения mb битов в направлении строки и сохранения N/(mb) битов в направлении столбцов, и выполненное с возможностью записи кодовых битов для кода LDPC (код с малой плотностью проверки на четность), имеющего длину кода N битов, подаваемых в него, в направлении столбцов для сохранения кодовых битов в направлении строки и в направлении столбца и считывания m битов кодовых битов LDPC в направлении строки, при этом m битов кодовых битов для кода LDPC установлены как один символ и b представляет собой заданное положительное целое число; и

средство замены, соединенное с запоминающим устройством и выполненное с возможностью замены mb кодовых битов таким образом, что кодовые биты после замены формируют биты символов, представляющие символы, в случае, когда mb кодовых битов, считанных в направлении строки упомянутого средства сохранения, установлены как b символов,

в котором код LDPC представляет собой код LDPC, предписанный в соответствии со стандартом DVB-S.2 или DVB-T.2, который имеет длину N кода 16200 битов и скорость кодирования 8/9;

m битов представляют собой 10, в то время как целое число b равно 2;

10 битов из кодовых битов отображают как один символ на некоторые из 1024 точек сигнала, предписанных в соответствии с 1024QAM (квадратурная амплитудная модуляция); и

упомянутое запоминающее устройство имеет 20 столбцов для сохранения 10´2 битов в направлении строки и содержит N/(10´2) битов в направлении столбцов;

упомянутое средство замены выполнено с возможностью замены для назначения

бита b0 для бита y8,

бита b1 для бита у3,

бита b2 для бита у7,

бита b3 для бита у10,

бита b4 для бита y19,

бита b5 для бита y4,

бита b6 для бита у9,

бита b7 для бита y5,

бита b8 для бита у17,

бита b9 для бита y6,

бита b10 для бита у14,

бита b11 для бита у11,

бита b12 для бита y2,

бита b13 для бита y18,

бита b14 для бита y16,

бита b15 для бита y15,

бита b16 для бита у0,

бита b17 для бита у1,

бита b18 для бита у13,

бита b19 для бита у12

для кода LDPC с длиной N кода 16200 битов и скоростью кодирования 8/9, когда i+1-й бит от старшего значащего бита 10´2 кодовых битов, считываемых в направлении строки упомянутого средства сохранения, представлен как бит bi и i+1-й бит от старшего значащего бита 10´2 битов символов одного символа представлен как бит yi.

7. Демультиплексор, содержащий

запоминающее устройство, имеющее емкость накопителя, требуемую для сохранения mb битов в направлении строки и сохранения N/(mb) битов в направлении столбцов, и выполненное с возможностью записи кодовых битов для кода LDPC (код с малой плотностью проверки на четность), имеющего длину кода N битов, подаваемых в него, в направлении столбцов для сохранения кодовых битов в направлении строки и в направлении столбца и считывания m битов кодовых битов LDPC в направлении строки, при этом m битов кодовых битов для кода LDPC установлены как один символ и b представляет собой заданное положительное целое число; и

средство замены, соединенное с запоминающим устройством и выполненное с возможностью замены mb кодовых битов таким образом, что кодовые биты после замены формируют биты символов, представляющие символы, в случае, когда mb кодовых битов, считанных в направлении строки упомянутого средства сохранения, установлены как b символов,

в котором код LDPC представляет собой код LDPC, предписанный в соответствии со стандартом DVB-S.2 или DVB-T.2, который имеет длину N кода 16200 битов и скорость кодирования 5/6 или 8/9;

m битов представляют собой 12, в то время как целое число b равно 2;

12 битов из кодовых битов отображают как один символ на некоторые из 4096 точек сигнала, предписанных в соответствии с 4096 QAM (квадратурная амплитудная модуляция); и

упомянутое запоминающее устройство имеет 24 столбца для сохранения 12´2 битов в направлении строки и содержит N/(12´2) битов в направлении столбцов;

упомянутое средство замены выполнено с возможностью замены для назначения

бита b0 для бита у10,

бита b1 для бита y15,

бита b2 для бита у4,

бита b3 для бита y19,

бита b4 для бита у21,

бита b5 для бита y16,

бита b6 для бита у23,

бита b7 для бита у18,

бита b8 для бита у11,

бита b9 для бита у14,

бита b10 для бита у22,

бита b11 для бита у5,

бита b12 для бита y6,

бита b13 для бита у17,

бита b14 для бита у13,

бита b15 для бита у20,

бита b16 для бита у1,

бита b17 для бита у3,

бита b18 для бита у9,

бита b19 для бита у2,

бита b20 для бита у7,

бита b21 для бита y8,

бита b22 для бита y12,

бита b23 для бита у0

для кода LDPC с длиной N кода 16200 битов и скоростью кодирования 5/6 или 8/9, когда i+1-й бит от старшего значащего бита 12´2 кодовых битов, считываемых в направлении строки упомянутого средства сохранения, представлен как бит bi и i+1-й бит от старшего значащего бита 12´2 битов символа двух последовательных символов представлен как бит yi.

8. Демультиплексор, содержащий

запоминающее устройство, имеющее емкость накопителя, требуемую для сохранения mb битов в направлении строки и сохранения N/(mb) битов в направлении столбцов, и выполненное с возможностью записи кодовых битов для кода LDPC (код с малой плотностью проверки на четность), имеющего длину кода N битов, подаваемых в него, в направлении столбцов для сохранения кодовых битов в направлении строки и в направлении столбца и считывания m битов кодовых битов LDPC в направлении строки, при этом m битов кодовых битов для кода LDPC установлены как один символ и b представляет собой заданное положительное целое число; и

средство замены, соединенное с запоминающим устройством и выполненное с возможностью замены mb кодовых битов таким образом, что кодовые биты после замены формируют биты символов, представляющие символы, в случае, когда mb кодовых битов, считанных в направлении строки упомянутого средства сохранения, установлены как b символов,

в котором код LDPC представляет собой код LDPC, предписанный в соответствии со стандартом DVB-S.2 или DVB-T.2, который имеет длину N кода 16200 битов и скорость кодирования 5/6;

m битов представляют собой 12, в то время как целое число b равно 2;

12 битов из кодовых битов отображают как один символ на некоторые из 4096 точек сигнала, предписанных в соответствии с 4096QAM (квадратурная амплитудная модуляция); и

упомянутое запоминающее устройство имеет 24 столбца для сохранения 12´2 битов в направлении строки и содержит N/(12´2) битов в направлении столбцов;

упомянутое средство замены выполнено с возможностью замены для назначения

бита b0 для бита у10,

бита b1 для бита y15,

бита b2 для бита y4,

бита b3 для бита y19,

бита b4 для бита у21,

бита b5 для бита y16,

бита b6 для бита у23,

бита b7 для бита y18,

бита b8 для бита у11,

бита b9 для бита у14,

бита b10 для бита у22,

бита b11 для бита y5,

бита b12 для бита y6,

бита b13 для бита у17,

бита b14 для бита у13,

бита b15 для бита у20,

бита b16 для бита у1,

бита b17 для бита у3,

бита b18 для бита у9,

бита b19 для бита y2,

бита b20 для бита у7,

бита b21 для бита y8,

бита b22 для бита у12,

бита b23 для бита у0

для кода LDPC с длиной N кода 16200 битов и скоростью кодирования 5/6, когда i+1-й бит от старшего значащего бита 12´2 кодовых битов, считываемых в направлении строки упомянутого средства сохранения, представлен как бит bi и i+1-й бит от старшего значащего бита 12´2 битов символа двух последовательных символов представлен как бит yi.

9. Демультиплексор, содержащий

запоминающее устройство, имеющее емкость накопителя, требуемую для сохранения mb битов в направлении строки и сохранения N/(mb) битов в направлении столбцов, и выполненное с возможностью записи кодовых битов для кода LDPC (код с малой плотностью проверки на четность), имеющего длину кода N битов, подаваемых в него, в направлении столбцов для сохранения кодовых битов в направлении строки и в направлении столбца и считывания m битов кодовых битов LDPC в направлении строки, при этом m битов кодовых битов для кода LDPC установлены как один символ и b представляет собой заданное положительное целое число; и

средство замены, соединенное с запоминающим устройством и выполненное с возможностью замены mb кодовых битов таким образом, что кодовые биты после замены формируют биты символов, представляющие символы, в случае, когда mb кодовых битов, считанных в направлении строки упомянутого средства сохранения, установлены как b символов,

в котором код LDPC представляет собой код LDPC, предписанный в соответствии со стандартом DVB-S.2 или DVB-T.2, который имеет длину N кода 16200 битов и скорость кодирования 8/9;

m битов представляют собой 12, в то время как целое число b равно 2;

12 битов из кодовых битов отображают как один символ на некоторые из 4096 точек сигнала, предписанных в соответствии с 4096QAM (квадратурная амплитудная модуляция); и

упомянутое запоминающее устройство имеет 24 столбца для сохранения 12´2 битов в направлении строки и содержит N/(12´2) битов в направлении столбцов;

упомянутое средство замены выполнено с возможностью замены для назначения

бита b0 для бита у10,

бита b1 для бита у15,

бита b2 для бита y4,

бита b3 для бита y19,

бита b4 для бита у21,

бита b5 для бита у16,

бита b6 для бита у23,

бита b7 для бита у18,

бита b8 для бита у11,

бита b9 для бита у14,

бита b10 для бита y22,

бита b11 для бита y5,

бита b12 для бита y6,

бита b13 для бита у17,

бита b14 для бита у13,

бита b15 для бита у20,

бита b16 для бита у1,

бита b17 для бита у3,

бита b18 для бита у9,

бита b19 для бита y2,

бита b20 для бита у7,

бита b21 для бита y8,

бита b22 для бита у12,

бита b23 для бита у0

для кода LDPC с длиной N кода 16200 битов и скоростью кодирования 8/9, когда i+1-й бит от старшего значащего бита 12´2 кодовых битов, считываемых в направлении строки упомянутого средства сохранения, представлен как бит bi и i+1-й бит от старшего значащего бита 12´2 битов символа двух последовательных символов представлен как бит yi.

10. Способ демультиплексирования, выполняемый демультиплексором по п.1, содержащий этапы, на которых

записывают кодовые биты для кода LDPC (код с малой плотностью проверки на четность), имеющего длину кода N битов в направлении столбцов для сохранения кодовых битов в направлении строки и в направлении столбца запоминающего устройства, имеющего емкость накопителя, требуемую для сохранения mb битов в направлении строки и сохранения N/(mb) битов в направлении столбцов;

считывают m битов кодовых битов LDPC в направлении строки, при этом m битов кодовых битов для кода LDPC установлены как один символ и b представляет собой заданное положительное целое число; и

осуществляют замену mb кодовых битов таким образом, что кодовые биты после замены формируют биты символов, представляющие символы, в случае, когда mb кодовых битов, считанных в направлении строки упомянутого средства сохранения, установлены как b символов,

в котором код LDPC представляет собой код LDPC, предписанный в соответствии со стандартом DVB-S.2 или DVB-T.2, который имеет длину N кода 64800 битов и скорость кодирования 5/6 или 9/10;

m битов представляют собой 12, в то время как целое число b равно 1;

12 битов из кодовых битов отображают как один символ на некоторые из 4096 точек сигнала, предписанных в соответствии с 4096QAM (квадратурная амплитудная модуляция);

упомянутое запоминающее устройство имеет 12 столбцов для сохранения 12´1 битов в направлении строки и содержит 64800/(12´1) битов в направлении столбцов;

на упомянутом этапе замены выполняют замену для назначения

бита b0 для бита y8,

бита b1 для бита у0,

бита b2 для бита y6,

бита b3 для бита у1,

бита b4 для бита y4,

бита b5 для бита y5,

бита b6 для бита y2,

бита b7 для бита у3,

бита b8 для бита y7,

бита b9 для бита у10,

бита b10 для бита у11,

бита b11 для бита у9

как для кода LDPC со скоростью кодирования 5/6, так и для кода LDPC со скоростью кодирования 9/10, когда i+1-й бит от старшего значащего бита 12´1 кодовых битов, считываемых в направлении строки упомянутого средства сохранения, представлен как бит bi и i+1-й бит от старшего значащего бита 12´1 битов символа одного символа представлен как бит yi.

11. Способ демультиплексирования, выполняемый демультиплексором по п.2, содержащий этапы, на которых

записывают кодовые биты для кода LDPC (код с малой плотностью проверки на четность), имеющего длину кода N битов, в направлении столбцов для сохранения кодовых битов в направлении строки и в направлении столбца запоминающего устройства, имеющего емкость накопителя, требуемую для сохранения mb битов в направлении строки и сохранения N/(mb) битов в направлении столбцов;

считывают m битов кодовых битов LDPC в направлении строки, при этом m битов кодовых битов для кода LDPC установлены как один символ и b представляет собой заданное положительное целое число; и

осуществляют замену mb кодовых битов таким образом, что кодовые биты после замены формируют биты символов, представляющие символы, в случае, когда mb кодовых битов, считанных в направлении строки упомянутого средства сохранения, установлены как b символов,

в котором код LDPC представляет собой код LDPC, предписанный в соответствии со стандартом DVB-S.2 или DVB-T.2, который имеет длину N кода 64800 битов и скорость кодирования 9/10;

m битов представляют собой 12, в то время как целое число b равно 1;

12 битов из кодовых битов отображают как один символ на некоторые из 4096 точек сигнала, предписанных в соответствии с 4096QAM (квадратурная амплитудная модуляция);

упомянутое запоминающее устройство имеет 12 столбцов для сохранения 12´1 битов в направлении строки и содержит 64800/(12´1) битов в направлении столбцов;

на упомянутом этапе замены выполняют замену для назначения

бита b0 для бита y8,

бита b1 для бита у0,

бита b2 для бита y6,

бита b3 для бита у1,

бита b4 для бита y4,

бита b5 для бита y5,

бита b6 для бита y2,

бита b7 для бита у3,

бита b8 для бита y7,

бита b9 для бита у10,

бита b10 для бита у11,

бита b11 для бита у9

для кода LDPC со скоростью кодирования 9/10, когда i+1-й бит от старшего значащего бита 12´1 кодовых битов, считываемых в направлении строки упомянутого средства сохранения, представлен как бит bi и i+1-й бит от старшего значащего бита 12´1 битов символа одного символа представлен как бит yi.

12. Способ демультиплексирования, выполняемый демультиплексором по п.3, содержащий этапы, на которых

записывают кодовые биты для кода LDPC (код с малой плотностью проверки на четность), имеющего длину кода N битов, в направлении столбцов для сохранения кодовых битов в направлении строки и в направлении столбца запоминающего устройства, имеющего емкость накопителя, требуемую для сохранения mb битов в направлении строки и сохранения N/(mb) битов в направлении столбцов;

считывают m битов кодовых битов LDPC в направлении строки, при этом m битов кодовых битов для кода LDPC установлены как один символ и b представляет собой заданное положительное целое число; и

осуществляют замену mb кодовых битов таким образом, что кодовые биты после замены формируют биты символов, представляющие символы, в случае, когда mb кодовых битов, считанных в направлении строки упомянутого средства сохранения, установлены как b символов,

в котором код LDPC представляет собой код LDPC, предписанный в соответствии со стандартом DVB-S.2 или DVB-T.2, который имеет длину N кода 16200 битов и скорость кодирования 3/4, 5/6 или 8/9;

m битов представляют собой 10, в то время как целое число b равно 2;

10 битов из кодовых битов отображают как один символ на некоторые из 1024 точек сигнала, предписанных в соответствии с 1024QAM (квадратурная амплитудная модуляция);

упомянутое запоминающее устройство имеет 20 столбцов для сохранения 10´2 битов в направлении строки и содержит N/(10´2) битов в направлении столбцов;

на упомянутом этапе замены выполняют замену для назначения

бита b0 для бита y8,

бита b1 для бита у3,

бита b2 для бита у7,

бита b3 для бита у10,

бита b4 для бита y19,

бита b5 для бита y4,

бита b6 для бита у9,

бита b7 для бита y5,

бита b8 для бита у17,

бита b9 для бита y6,

бита b10 для бита у14,

бита b11 для бита у11,

бита b12 для бита у2,

бита b13 для бита y18,

бита b14 для бита y16,

бита b15 для бита y15,

бита b16 для бита у0,

бита b17 для бита у1

бита b18 для бита у13,

бита b19 для бита у12

для кода LDPC с длиной N кода 16200 битов и скоростью кодирования 3/4, 5/6 или 8/9, когда i+1-й бит от старшего значащего бита 10´2 кодовых битов, считываемых в направлении строки упомянутого средства сохранения, представлен как бит bi и i+1-й бит от старшего значащего бита 10´2 битов символа двух последовательных символов представлен как бит yi.

13. Способ демультиплексирования, выполняемый демультиплексором по п.4, содержащий этапы, на которых

записывают кодовые биты для кода LDPC (код с малой плотностью проверки на четность), имеющего длину кода N битов, в направлении столбцов для сохранения кодовых битов в направлении строки и в направлении столбца запоминающего устройства, имеющего емкость накопителя, требуемую для сохранения mb битов в направлении строки и сохранения N/(mb) битов в направлении столбцов;

считывают m битов кодовых битов LDPC в направлении строки, при этом m битов кодовых битов для кода LDPC установлены как один символ и b представляет собой заданное положительное целое число; и

осуществляют замену mb кодовых битов таким образом, что кодовые биты после замены формируют биты символов, представляющие символы, в случае, когда mb кодовых битов, считанных в направлении строки упомянутого средства сохранения, установлены как b символов,

в котором код LDPC представляет собой код LDPC, предписанный в соответствии со стандартом DVB-S.2 или DVB-T.2, который имеет длину N кода 16200 битов и скорость кодирования 3/4;

m битов представляют собой 10, в то время как целое число b равно 2;

10 битов из кодовых битов отображают как один символ на некоторые из 1024 точек сигнала, предписанных в соответствии с 1024QAM (квадратурная амплитудная модуляция);

упомянутое запоминающее устройство имеет 20 столбцов для сохранения 10´2 битов в направлении строки и содержит N/(10´2) битов в направлении столбцов;

на упомянутом этапе замены выполняют замену для назначения

бита b0 для бита y8,

бита b1 для бита у3,

бита b2 для бита у7,

бита b3 для бита у10,

бита b4 для бита y19,

бита b5 для бита y4,

бита b6 для бита у9,

бита b7 для бита y5,

бита b8 для бита у17,

бита b9 для бита y6,

бита b10 для бита у14,

бита b11 для бита у11,

бита b12 для бита y2,

бита b13 для бита у18,

бита b14 для бита y16,

бита b15 для бита y15,

бита b16 для бита у0,

бита b17 для бита у1,

бита b18 для бита у13,

бита b19 для бита y12

для кода LDPC с длиной N кода 16200 битов и скоростью кодирования 3/4, когда i+1-й бит от старшего значащего бита 10´2 кодовых битов, считываемых в направлении строки упомянутого средства сохранения, представлен как бит bi, и i+1-й бит от старшего значащего бита 10´2 битов символа двух последовательных символов представлен как бит yi.

14. Способ демультиплексирования, выполняемый демультиплексором по п.5, содержащий этапы, на которых

записывают кодовые биты для кода LDPC (код с малой плотностью проверки на четность), имеющего длину кода N битов, в направлении столбцов для сохранения кодовых битов в направлении строки и в направлении столбца запоминающего устройства, имеющего емкость накопителя, требуемую для сохранения mb битов в направлении строки и сохранения N/(mb) битов в направлении столбцов;

считывают m битов кодовых битов LDPC в направлении строки, при этом m битов кодовых битов для кода LDPC установлены как один символ и b представляет собой заданное положительное целое число; и

осуществляют замену mb кодовых битов таким образом, что кодовые биты после замены формируют биты символов, представляющие символы, в случае, когда mb кодовых битов, считанных в направлении строки упомянутого средства сохранения, установлены как b символов,

в котором код LDPC представляет собой код LDPC, предписанный в соответствии со стандартом DVB-S.2 или DVB-T.2, который имеет длину N кода 16200 битов и скорость кодирования 5/6;

m битов представляют собой 10 в то время как целое число b равно 2;

10 битов из кодовых битов отображают как один символ на некоторые из 1024 точек сигнала, предписанных в соответствии с 1024QAM (квадратурная амплитудная модуляция);

упомянутое запоминающее устройство имеет 20 столбцов для сохранения 10´2 битов в направлении строки и содержит N/(10´2) битов в направлении столбцов;

на упомянутом этапе замены выполняют замену для назначения

бита b0 для бита y8,

бита b1 для бита у3,

бита b2 для бита у7,

бита b3 для бита у10,

бита b4 для бита у19,

бита b5 для бита y4,

бита b6 для бита у9,

бита b7 для бита y5,

бита b8 для бита у17,

бита b9 для бита y6,

бита b10 для бита у14,

бита b11 для бита у11,

бита b12 для бита y2,

бита b13 для бита y18,

бита b14 для бита у16,

бита b15 для бита y15,

бита b16 для бита у0,

бита b17 для бита у1,

бита b18 для бита у13,

бита b19 для бита y12

для кода LDPC с длиной N кода 16200 битов и скоростью кодирования 5/6, когда i+1-й бит от старшего значащего бита 10´2 кодовых битов, считываемых в направлении строки упомянутого средства сохранения, представлен как бит bi и i+1-й бит от старшего значащего бита 10´2 битов символа двух последовательных символов представлен как бит yi.

15. Способ демультиплексирования, выполняемый демультиплексором по п.6, содержащий этапы, на которых

записывают кодовые биты для кода LDPC (код с малой плотностью проверки на четность), имеющего длину кода N битов, в направлении столбцов для сохранения кодовых битов в направлении строки и в направлении столбца запоминающего устройства, имеющего емкость накопителя, требуемую для сохранения mb битов в направлении строки и сохранения N/(mb) битов в направлении столбцов;

считывают m битов кодовых битов LDPC в направлении строки, при этом m битов кодовых битов для кода LDPC установлены как один символ и b представляет собой заданное положительное целое число; и

осуществляют замену mb кодовых битов таким образом, что кодовые биты после замены формируют биты символов, представляющие символы, в случае, когда mb кодовых битов, считанных в направлении строки упомянутого средства сохранения, установлены как b символов,

в котором код LDPC представляет собой код LDPC, предписанный в соответствии со стандартом DVB-S.2 или DVB-T.2, который имеет длину N кода 16200 битов и скорость кодирования 8/9;

m битов представляют собой 10, в то время как целое число b равно 2;

10 битов из кодовых битов отображают как один символ на некоторые из 1024 точек сигнала, предписанных в соответствии с 1024QAM (квадратурная амплитудная модуляция);

упомянутое запоминающее устройство имеет 20 столбцов для сохранения 10´2 битов в направлении строки и содержит N/(10´2) битов в направлении столбцов;

на упомянутом этапе замены выполняют замену для назначения

бита b0 для бита y8,

бита b1 для бита у3,

бита b2 для бита у7,

бита b3 для бита у10,

бита b4 для бита y19,

бита b5 для бита y4,

бита b6 для бита у9,

бита b7 для бита y5,

бита b8 для бита у17,

бита b9 для бита у6,

бита b10 для бита у14,

бита b11 для бита у11,

бита b12 для бита y2,

бита b13 для бита у18,

бита b14 для бита y16,

бита b15 для бита y15,

бита b16 для бита у0,

бита b17 для бита у1,

бита b18 для бита у13,

бита b19 для бита y12

для кода LDPC с длиной N кода 16200 битов и скоростью кодирования 8/9, когда i+1-й бит от старшего значащего бита 10´2 кодовых битов, считываемых в направлении строки упомянутого средства сохранения, представлен как бит bi и i+1-й бит от старшего значащего бита 10´2 битов символа двух последовательных символов представлен как бит yi.

16. Способ демультиплексирования, выполняемый демультиплексором по п.7, содержащий этапы, на которых

записывают кодовые биты для кода LDPC (код с малой плотностью проверки на четность), имеющего длину кода N битов, в направлении столбцов для сохранения кодовых битов в направлении строки и в направлении столбца запоминающего устройства, имеющего емкость накопителя, требуемую для сохранения mb битов в направлении строки и сохранения N/(mb) битов в направлении столбцов;

считывают m битов кодовых битов LDPC в направлении строки, при этом m битов кодовых битов для кода LDPC установлены как один символ и b представляет собой заданное положительное целое число; и

осуществляют замену mb кодовых битов таким образом, что кодовые биты после замены формируют биты символов, представляющие символы, в случае, когда mb кодовых битов, считанных в направлении строки упомянутого средства сохранения, установлены как b символов,

в котором код LDPC представляет собой код LDPC, предписанный в соответствии со стандартом DVB-S.2 или DVB-T.2, который имеет длину N кода 16200 битов и имеет скорость кодирования 5/6 или 8/9;

m битов представляют собой 12, в то время как целое число b равно 2;

12 битов из кодовых битов отображают как один символ на некоторые из 4096 точек сигнала, предписанных в соответствии с 4096QAM (квадратурная амплитудная модуляция);

упомянутое запоминающее устройство имеет 24 столбца для сохранения 12´2 битов в направлении строки и содержит N/(12´2) битов в направлении столбцов;

на упомянутом этапе замены выполняют замену для назначения

бита b0 для бита у10,

бита b1 для бита y15,

бита b2 для бита y4,

бита b3 для бита y19,

бита b4 для бита y21,

бита b5 для бита у16,

бита b6 для бита у23,

бита b7 для бита y18,

бита b8 для бита у11,

бита b9 для бита у14,

бита b10 для бита у22,

бита b11 для бита у5,

бита b12 для бита у6,

бита b13 для бита у17,

бита b14 для бита у13,

бита b15 для бита у20,

бита b16 для бита у1,

бита b17 для бита у3,

бита b18 для бита у9,

бита b19 для бита y2,

бита b20 для бита у7,

бита b21 для бита y8,

бита b22 для бита y12,

бита b23 для бита у0

для кода LDPC с длиной N кода 16200 битов и скоростью кодирования 5/6 или 8/9, когда i+1-й бит от старшего значащего бита 12´2 кодовых битов, считываемых в направлении строки упомянутого средства сохранения, представлен как бит bi и i+1-й бит от старшего значащего бита 12´2 битов символа двух последовательных символов представлен как бит yi.

17. Способ демультиплексирования, выполняемый демультиплексором по п.8, содержащий этапы, на которых

записывают кодовые биты для кода LDPC (код с малой плотностью проверки на четность), имеющего длину кода N битов, в направлении столбцов для сохранения кодовых битов в направлении строки и в направлении столбца запоминающего устройства, имеющего емкость накопителя, требуемую для сохранения mb битов в направлении строки и сохранения N/(mb) битов в направлении столбцов;

считывают m битов кодовых битов LDPC в направлении строки, при этом m битов кодовых битов для кода LDPC установлены как один символ и b представляет собой заданное положительное целое число; и

осуществляют замену mb кодовых битов таким образом, что кодовые биты после замены формируют биты символов, представляющие символы, в случае, когда mb кодовых битов, считанных в направлении строки упомянутого средства сохранения, установлены как b символов,

в котором код LDPC представляет собой код LDPC, предписанный в соответствии со стандартом DVB-S.2 или DVB-T.2, который имеет длину N кода 16200 битов и скорость кодирования 5/6;

m битов представляют собой 12, в то время как целое число b равно 2;

12 битов из кодовых битов отображают как один символ на некоторые из 4096 точек сигнала, предписанных в соответствии с 4096QAM (квадратурная амплитудная модуляция);

упомянутое запоминающее устройство имеет 24 столбца для сохранения 12´2 битов в направлении строки и содержит N/(12´2) битов в направлении столбцов;

на упомянутом этапе замены выполняют замену для назначения

бита b0 для бита у10,

бита b1 для бита у15,

бита b2 для бита y4,

бита b3 для бита y19,

бита b4 для бита у21,

бита b5 для бита y16,

бита b6 для бита у23,

бита b7 для бита у18,

бита b8 для бита у11,

бита b9 для бита у14,

бита b10 для бита у22,

бита b11 для бита y5,

бита b12 для бита y6,

бита b13 для бита у17,

бита b14 для бита у13,

бита b15 для бита у20,

бита b16 для бита у1,

бита b17 для бита у3,

бита b18 для бита у9,

бита b19 для бита у2,

бита b20 для бита у7,

бита b21 для бита y8,

бита b22 для бита у12,

бита b23 для бита у0

для кода LDPC с длиной N кода 16200 битов и скоростью кодирования 5/6, когда i+1-й бит от старшего значащего бита 12´2 кодовых битов, считываемых в направлении строки упомянутого средства сохранения, представлен как бит bi и i+1-й бит от старшего значащего бита 12´2 битов символа двух последовательных символов представлен как бит yi.

18. Способ демультиплексирования, выполняемый демультиплексором по п.9, содержащий этапы, на которых

записывают кодовые биты для кода LDPC (код с малой плотностью проверки на четность), имеющего длину кода N битов, в направлении столбцов для сохранения кодовых битов в направлении строки и в направлении столбца запоминающего устройства, имеющего емкость накопителя, требуемую для сохранения mb битов в направлении строки и сохранения N/(mb) битов в направлении столбцов;

считывают m битов кодовых битов LDPC в направлении строки, при этом m битов кодовых битов для кода LDPC установлены как один символ и b представляет собой заданное положительное целое число; и

осуществляют замену mb кодовых битов таким образом, что кодовые биты после замены формируют биты символов, представляющие символы, в случае, когда mb кодовых битов, считанных в направлении строки упомянутого средства сохранения, установлены как b символов,

в котором код LDPC представляет собой код LDPC, предписанный в соответствии со стандартом DVB-S.2 или DVB-T.2, который имеет длину N кода 16200 битов и скорость кодирования 8/9;

m битов представляют собой 12, в то время как целое число b равно 2;

12 битов из кодовых битов отображают как один символ на некоторые из 4096 точек сигнала, предписанных в соответствии с 4096QAM (квадратурная амплитудная модуляция);

упомянутое запоминающее устройство имеет 24 столбца для сохранения 12´2 битов в направлении строки и содержит N/(12´2) битов в направлении столбцов;

на упомянутом этапе замены выполняют замену для назначения

бита b0 для бита у10,

бита b1 для бита у15,

бита b2 для бита y4,

бита b3 для бита y19,

бита b4 для бита у21,

бита b5 для бита y16,

бита b6 для бита у23,

бита b7 для бита y18,

бита b8 для бита у11,

бита b9 для бита у14,

бита b10 для бита y22,

бита b11 для бита y5,

бита b12 для бита y6,

бита b13 для бита у17,

бита b14 для бита у13,

бита b15 для бита у20,

бита b16 для бита у1,

бита b17 для бита у3,

бита b18 для бита у9,

бита b19 для бита y2,

бита b20 для бита у7,

бита b21 для бита y8,

бита b22 для бита y12,

бита b23 для бита у0

для кода LDPC с длиной N кода 16200 битов и скоростью кодирования 8/9, когда i+1-й бит от старшего значащего бита 12´2 кодовых битов, считываемых в направлении строки упомянутого средства сохранения, представлен как бит bi и i+1-й бит от старшего значащего бита 12´2 битов символа двух последовательных символов представлен как бит yi.

Текст