Устройство и способ обработки данных, а также кодирующее устройство и способ кодирования

Номер патента: 21966

Опубликовано: 30.10.2015

Авторы: Ямамото Макико, Окада Сатоси, Ёкокава Такаси, Икегая Рьёдзи

Формула / Реферат

1. Устройство обработки данных, содержащее

запоминающее устройство, имеющее емкость накопителя для сохранения mb битов в направлении строки и сохранения N/(mb) битов в направлении столбцов и выполненное с возможностью записи кодовых битов кода LDPC (низкой плотности с контролем четности), имеющего длину кода в N битов, подаваемых в него, в направлении столбца для хранения кодовых битов в направлении строки и в направлении столбца, и считывания m битов из кодовых битов кода LDPC в направлении строки, при этом m битов кодовых битов для кода LDPC установлены как один символ и b представляет собой заданное положительное целое число; и

средство замены, соединенное с запоминающим устройством и выполненное с возможностью замены mb кодовых битов, чтобы эти кодовые биты после замены образовали биты символов, представляющие символы, когда mb кодовых разрядов, считанных в направлении строки запоминающего устройства, устанавливаются в качестве b символов;

в котором код LDPC является кодом LDPC, который имеет длину кода N, равную 64.800, и имеет скорость кодирования 2/3;

m битов равны 8 битам, тогда как целое число b равно 2;

8 кодовых битов отображаются в качестве одного символа в одну из 256 сигнальных точек, предписанных в 256QAM (квадратурная амплитудная модуляция);

упомянутое запоминающее устройство имеет 16 столбцов для хранения 8´2 битов в направлении строки и хранения 64.800/(8´2) битов в направлении столбца; и

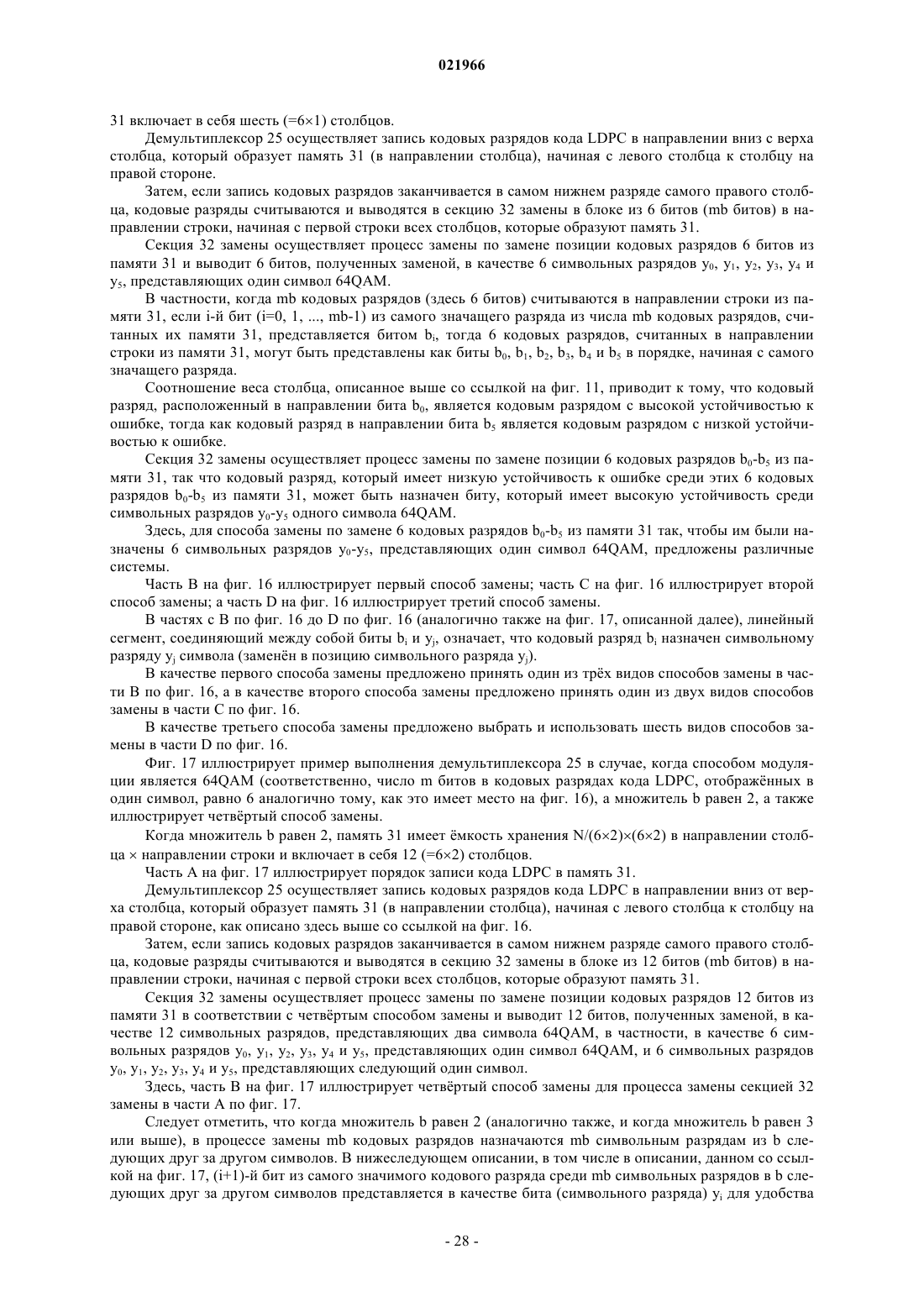

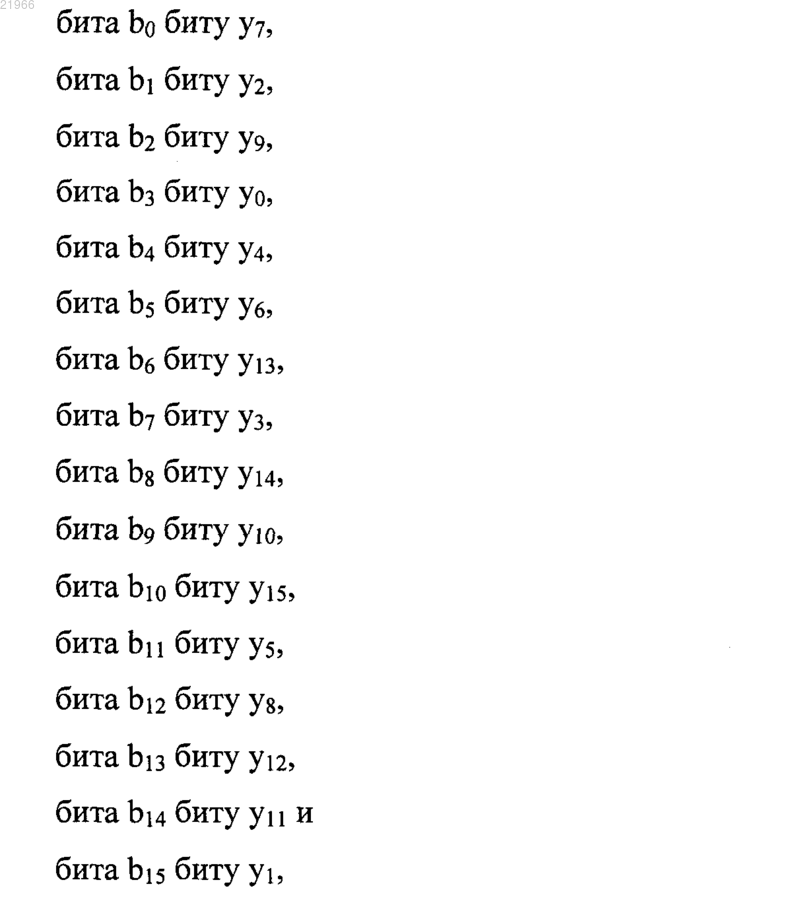

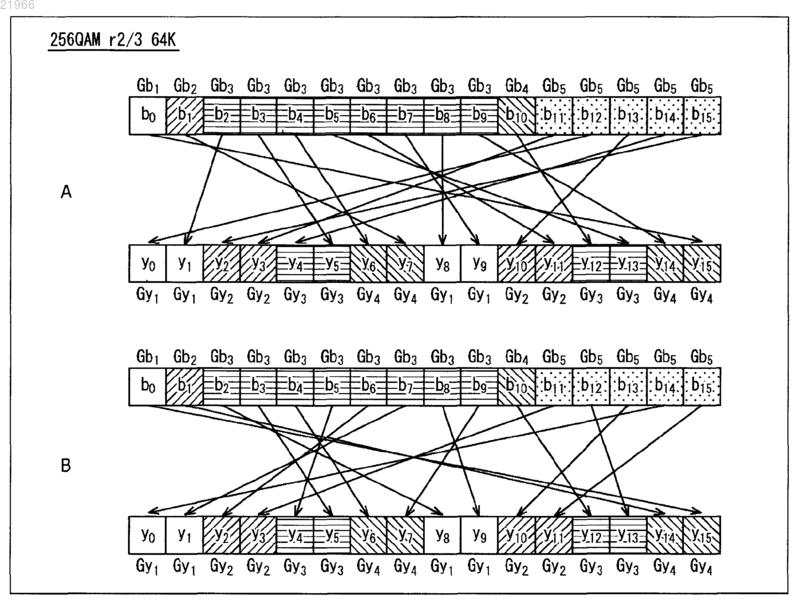

упомянутое средство замены выполнено с возможностью замены для назначения

когда (i+1)-й бит из старшего значащего бита из 8´2 кодовых битов, считанных в направлении строки запоминающего устройства, представляется как бит bi, a (i+1)-й бит из старшего значащего бита из 8´2 битов символов двух следующих друг за другом символов представляется как бит yi;

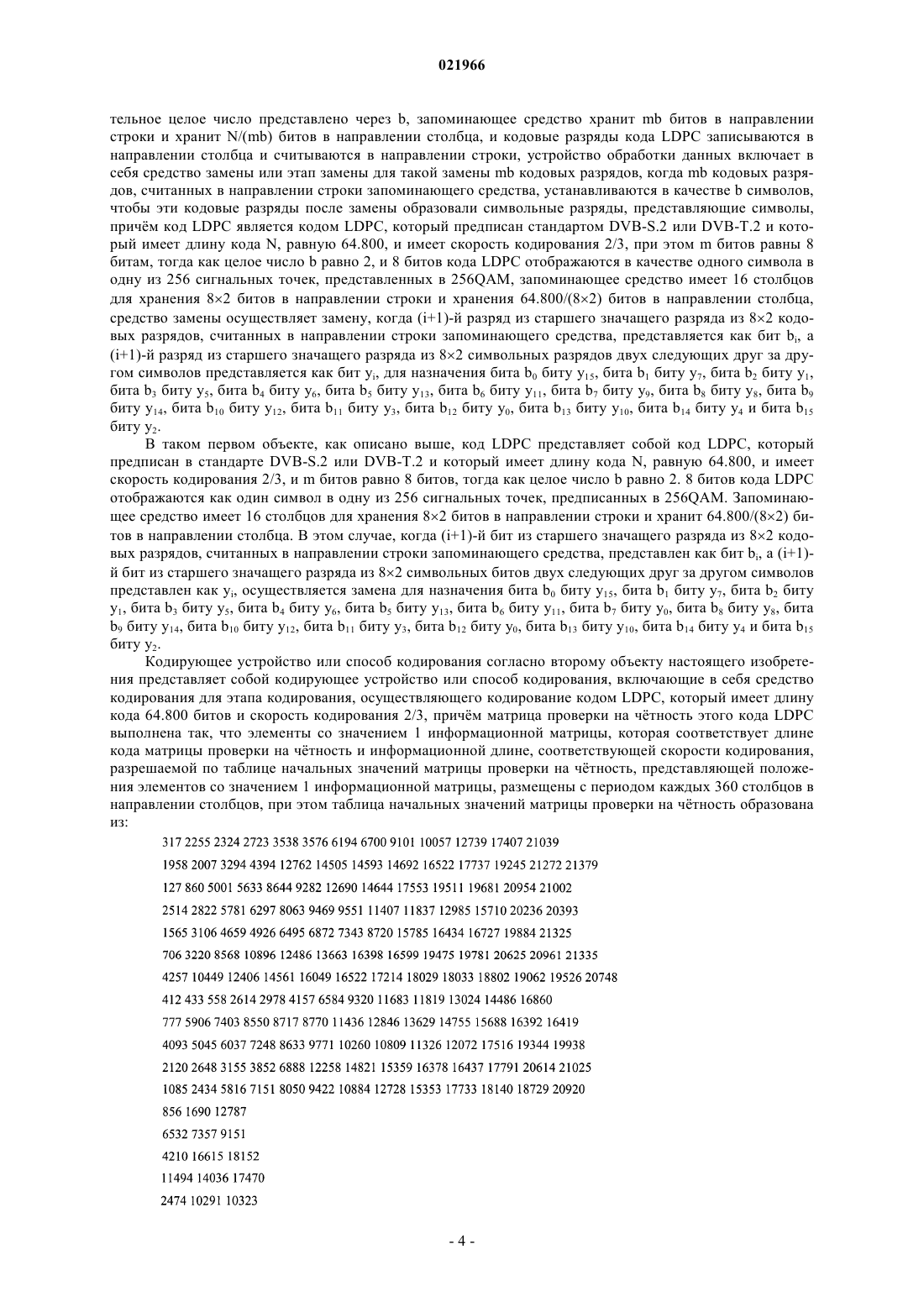

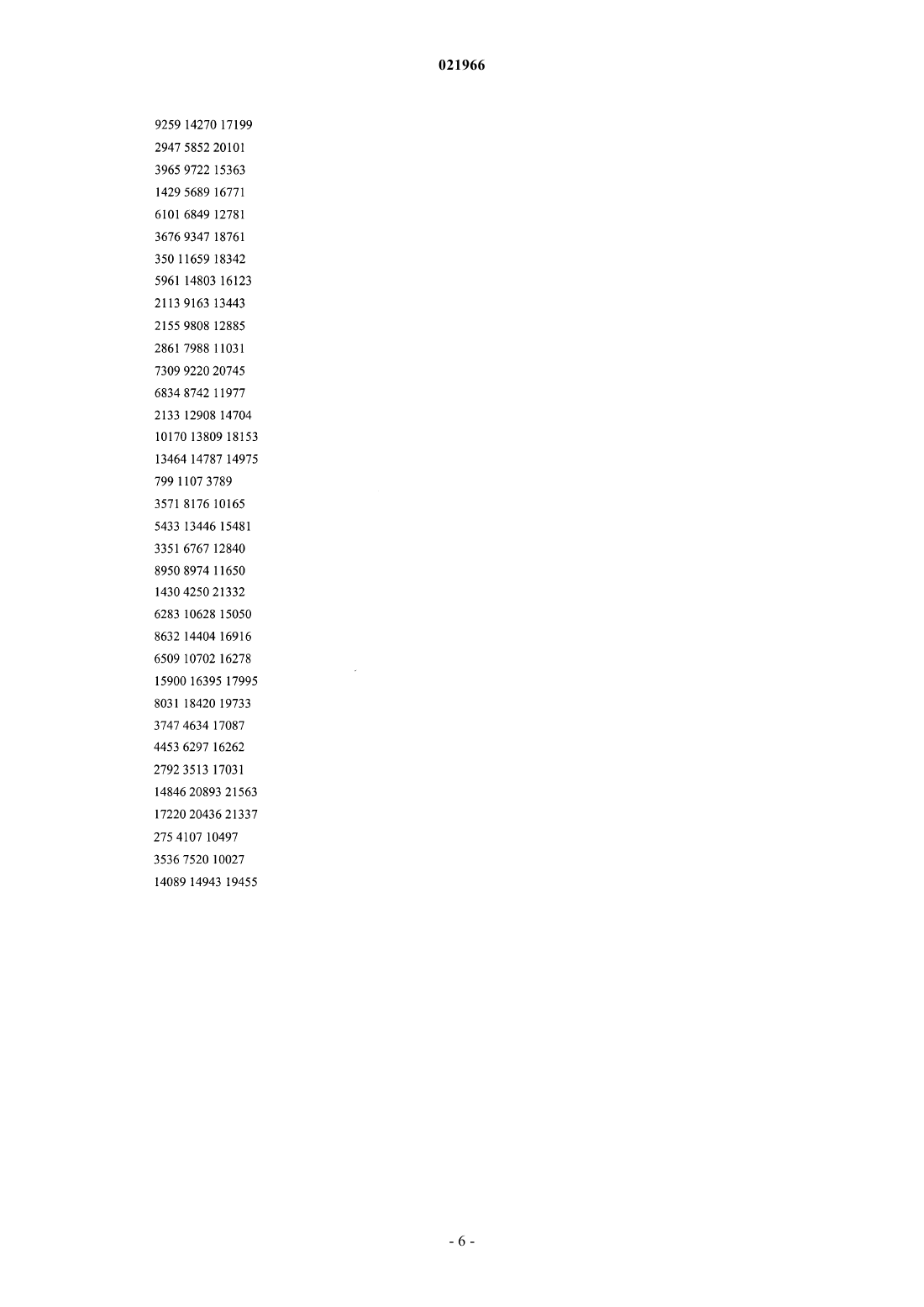

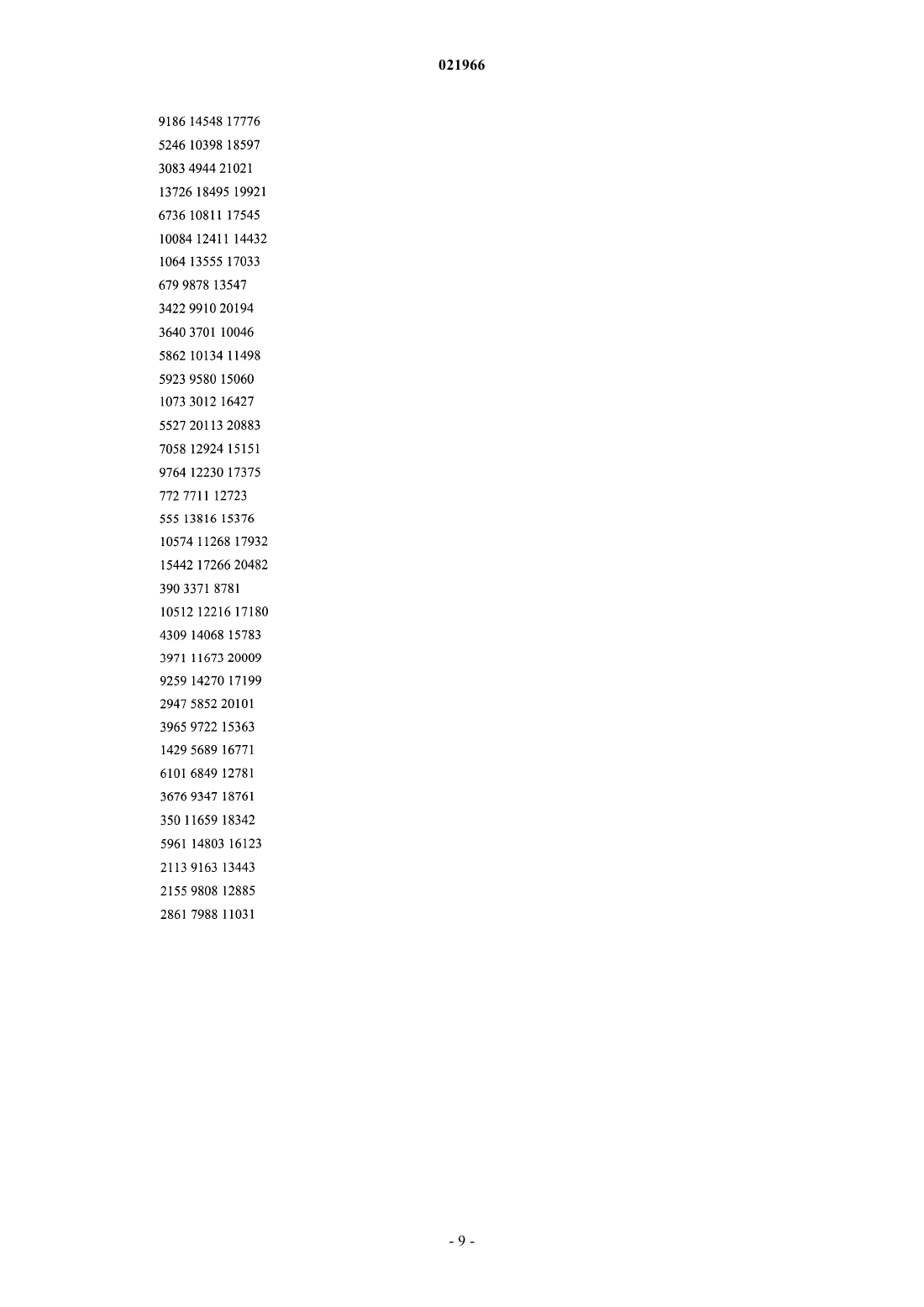

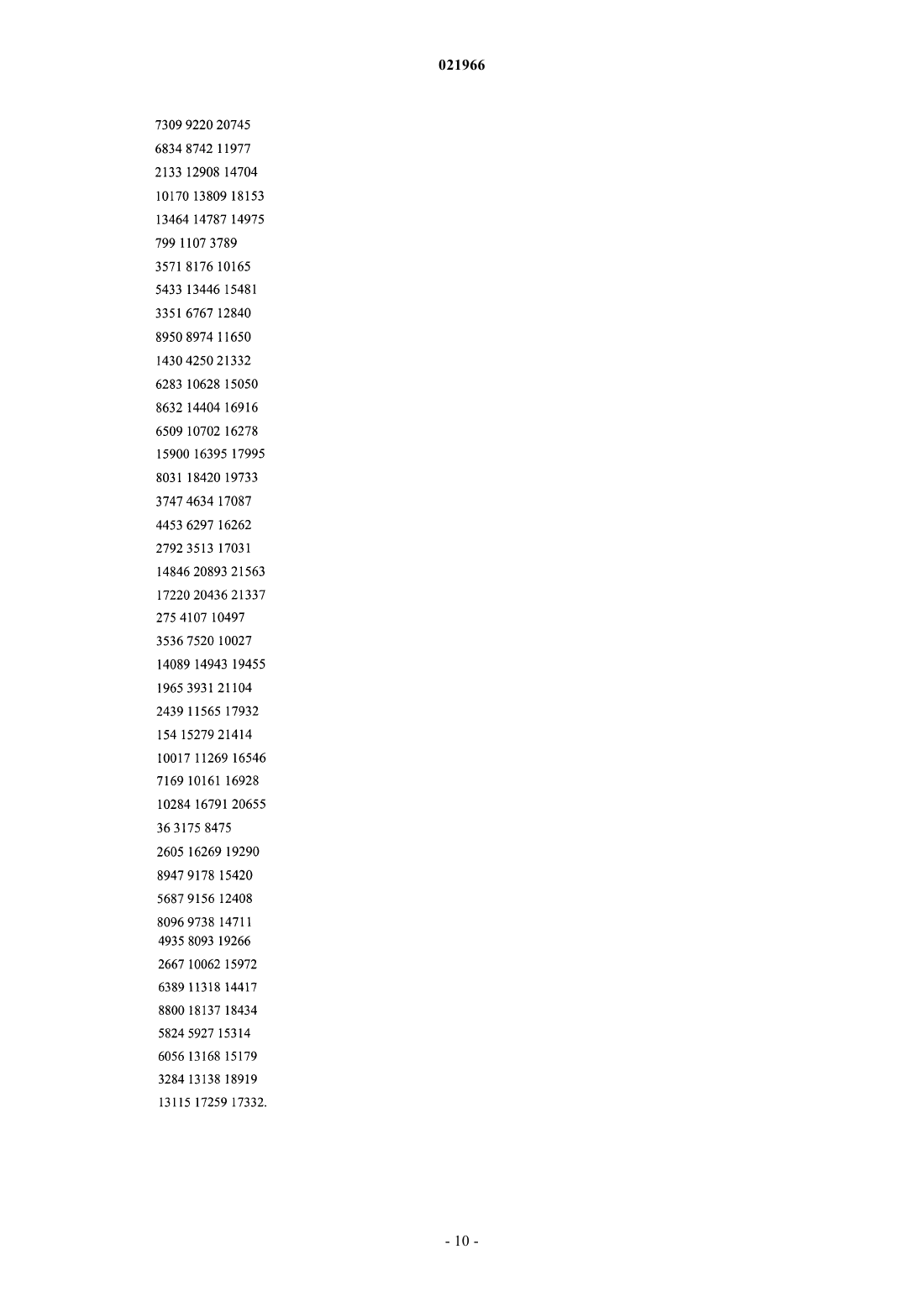

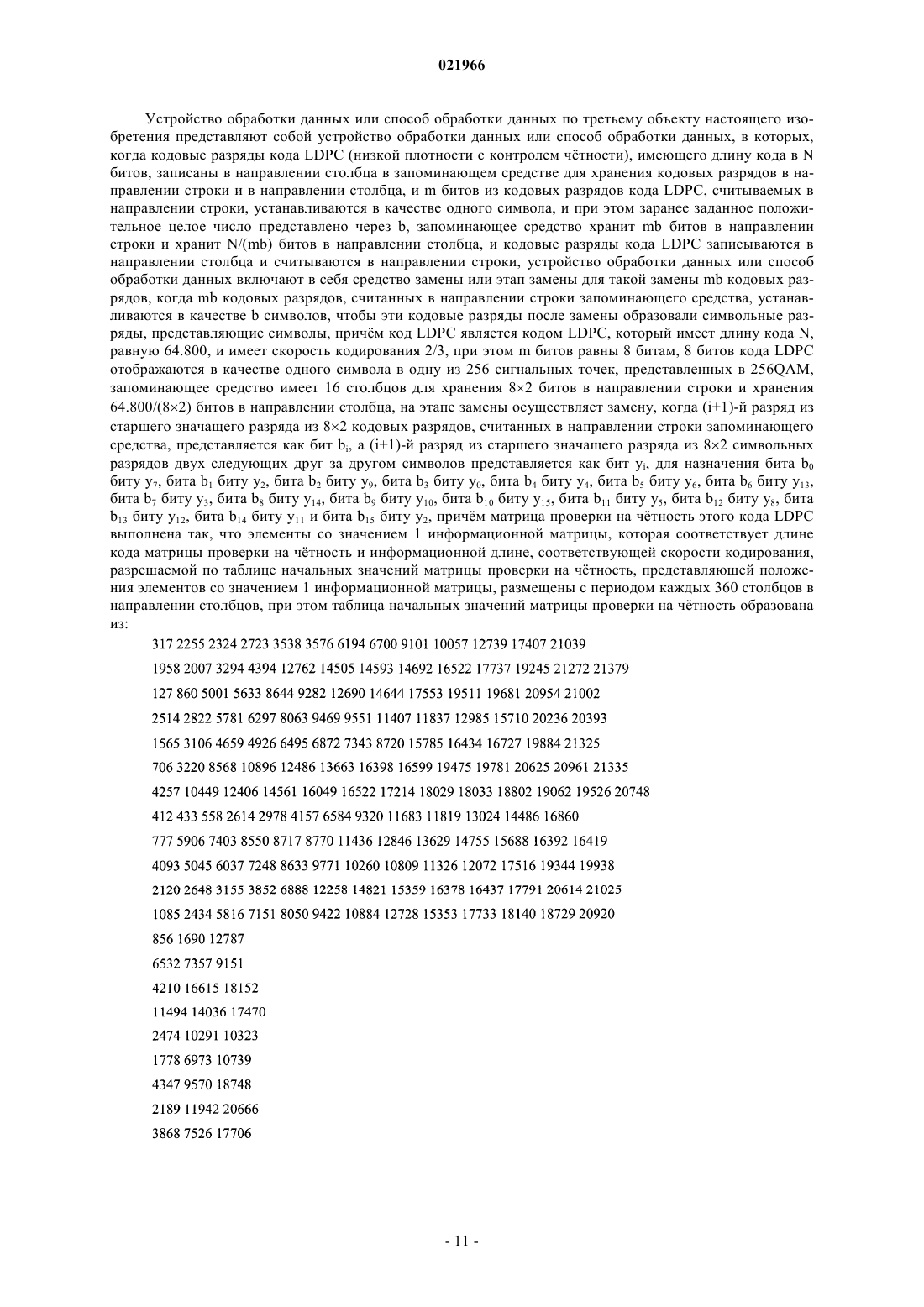

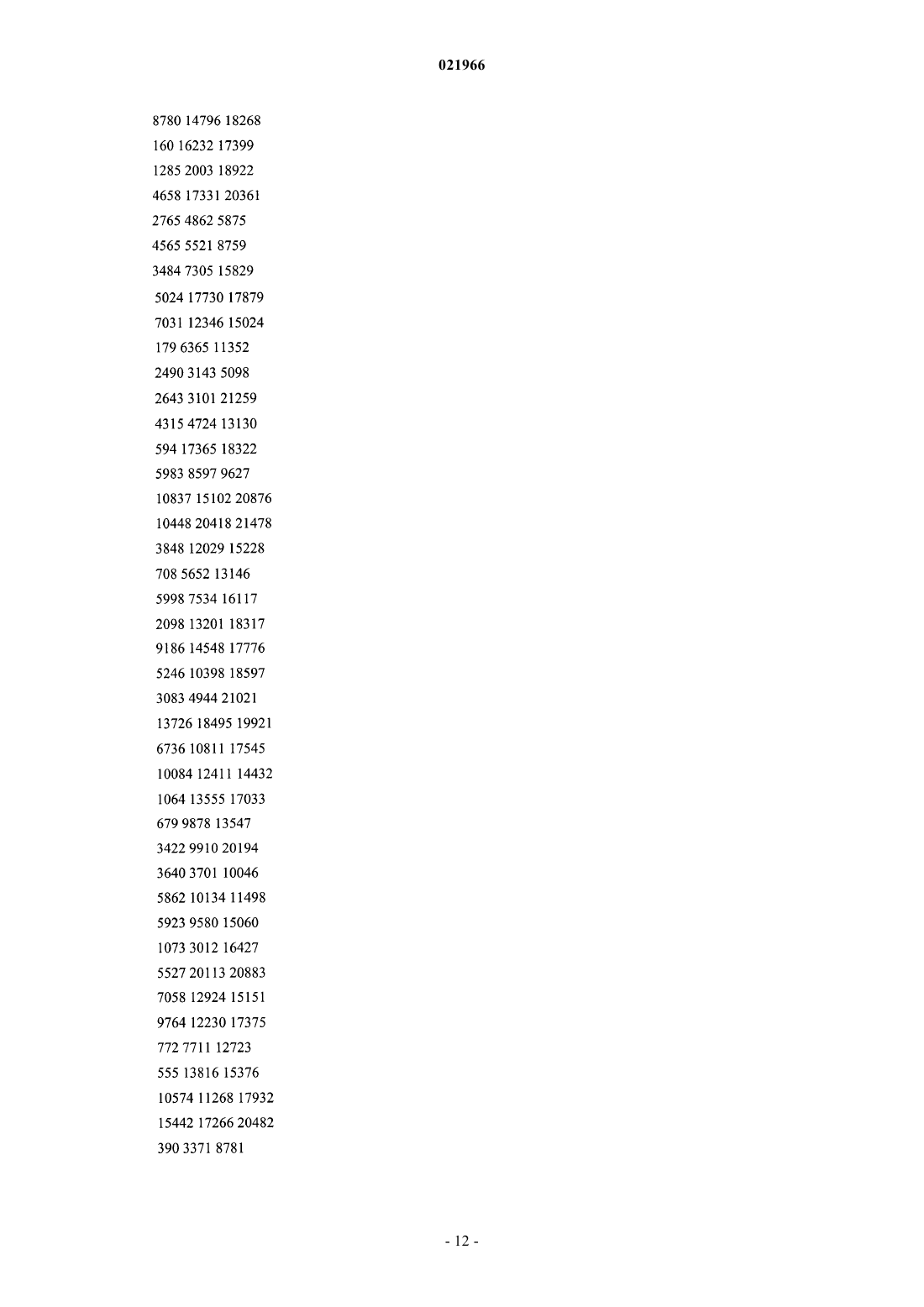

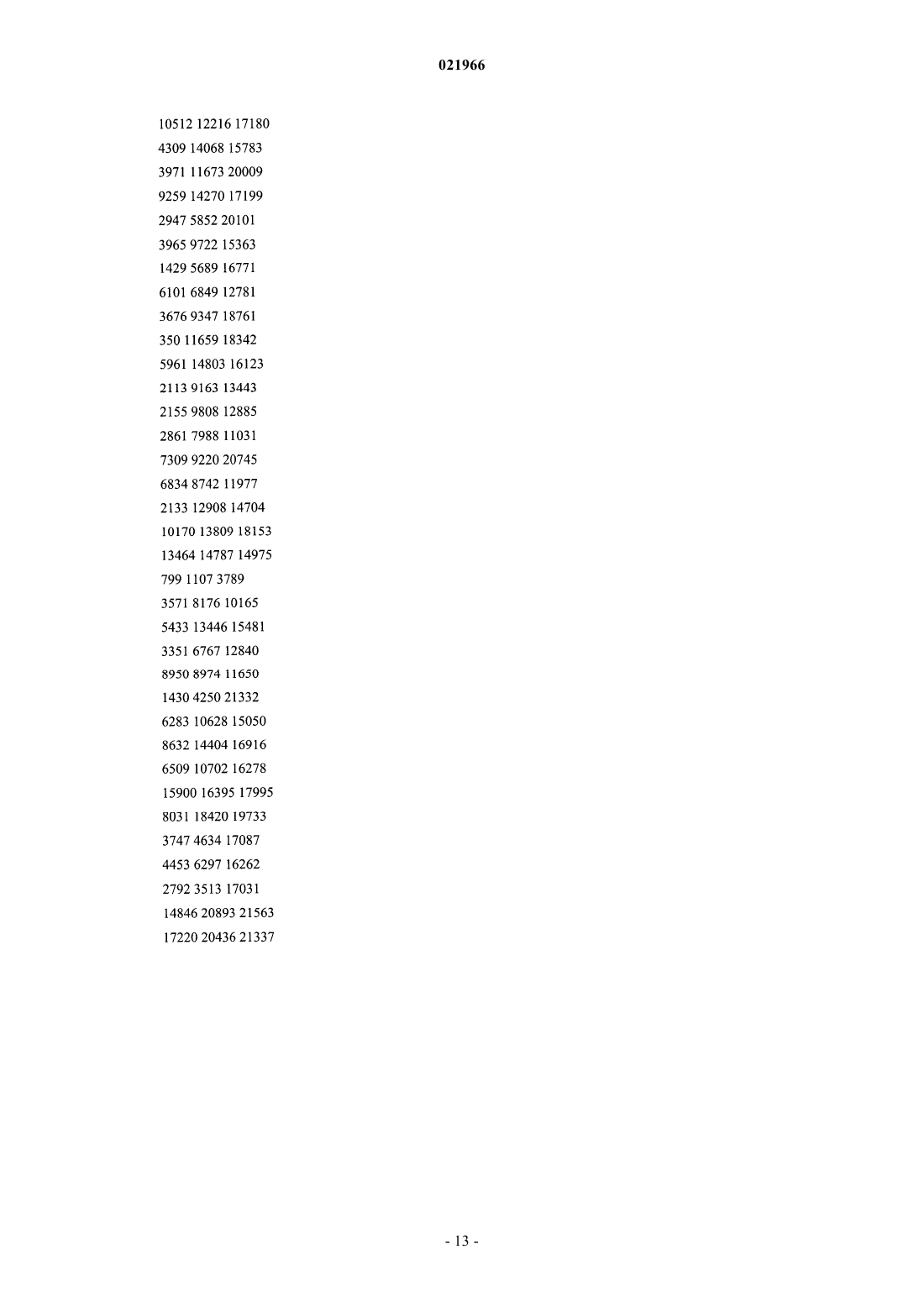

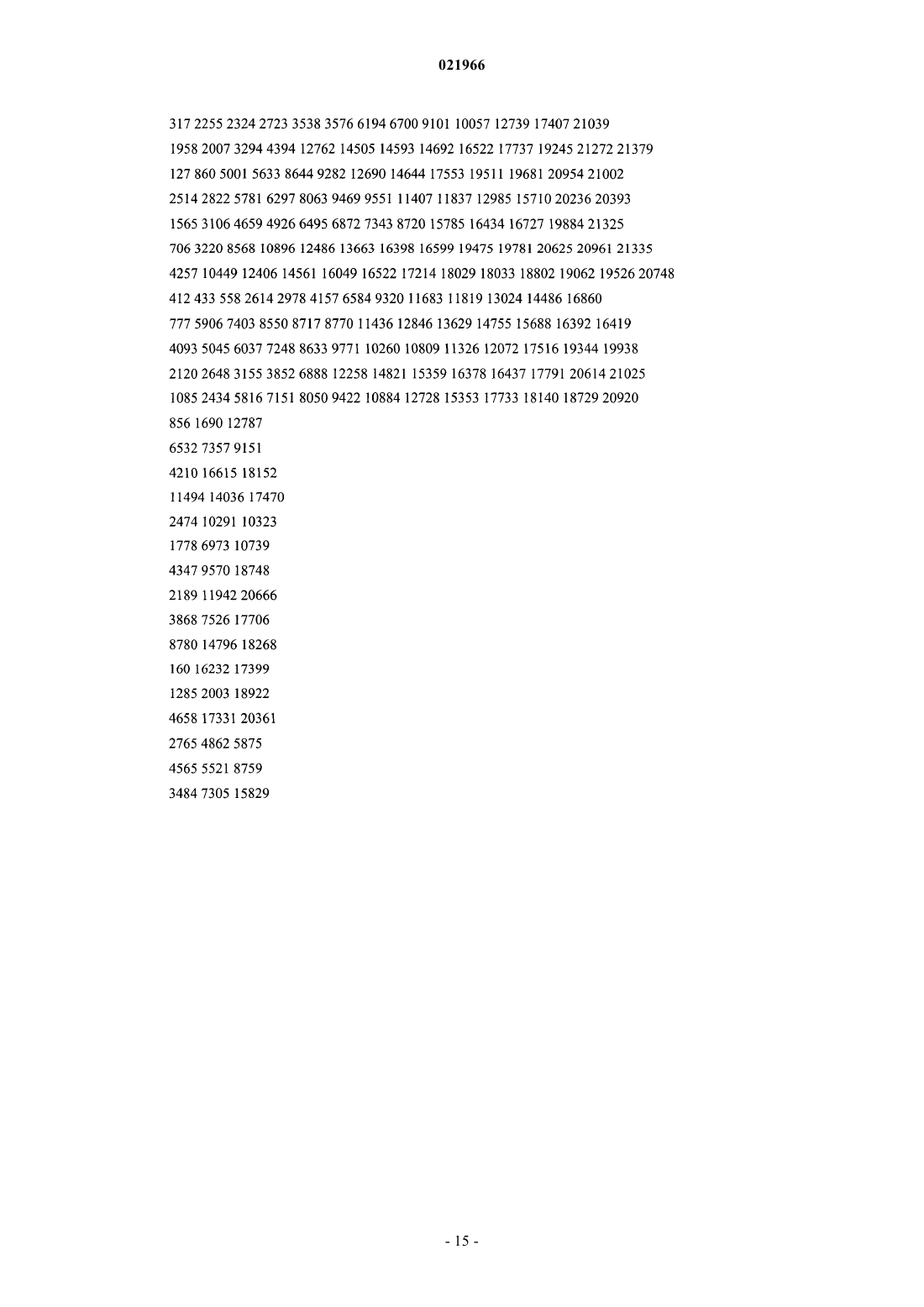

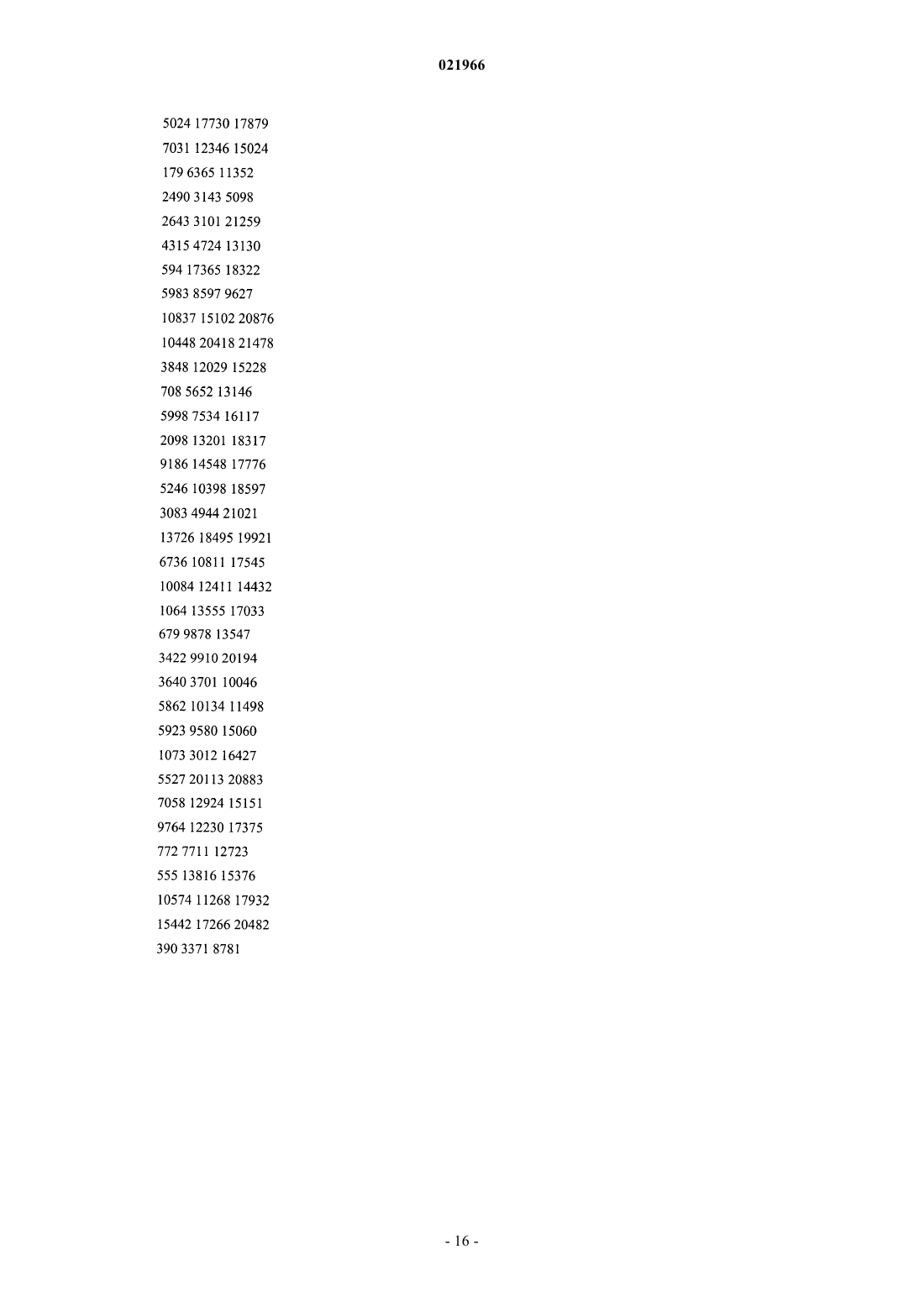

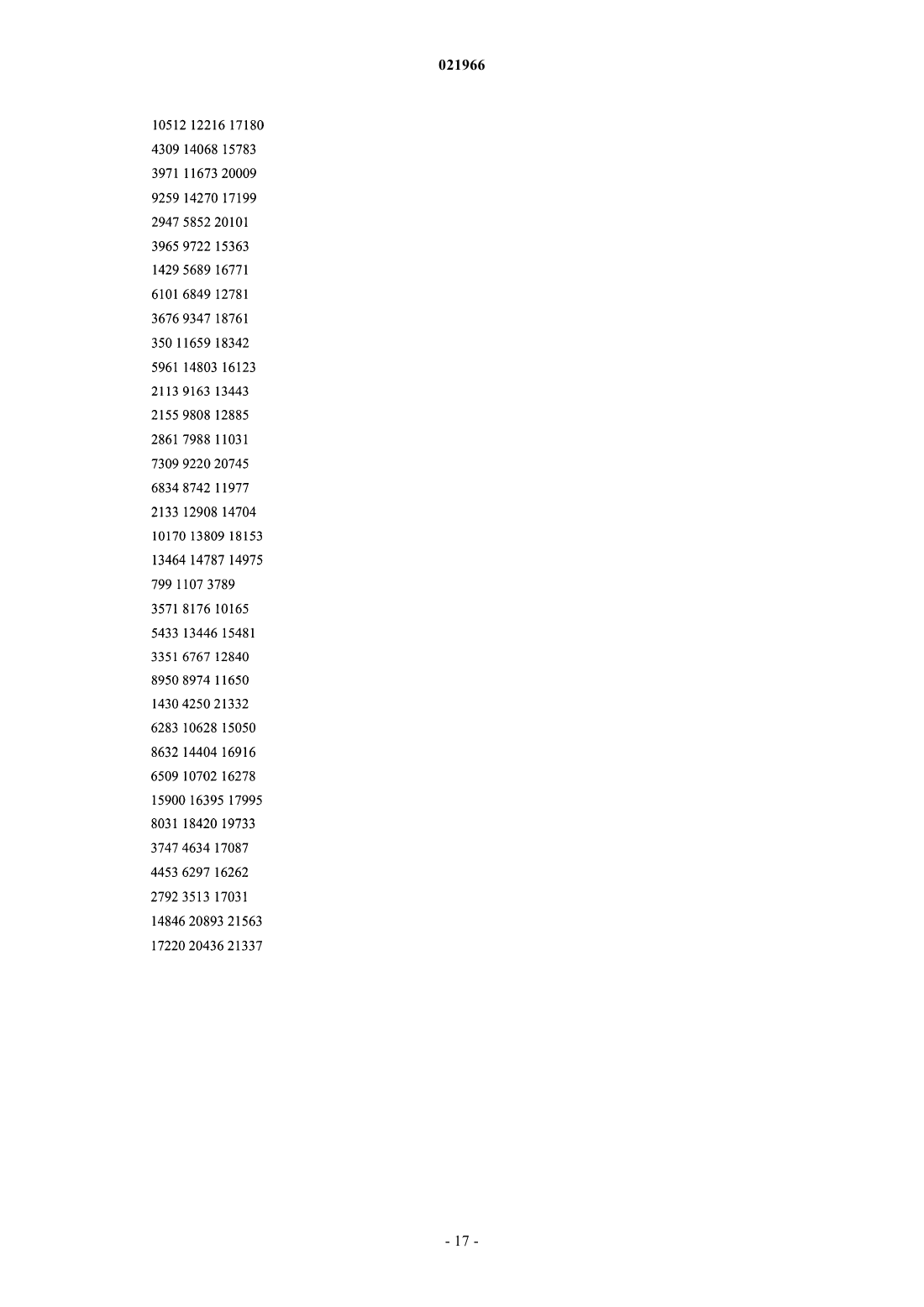

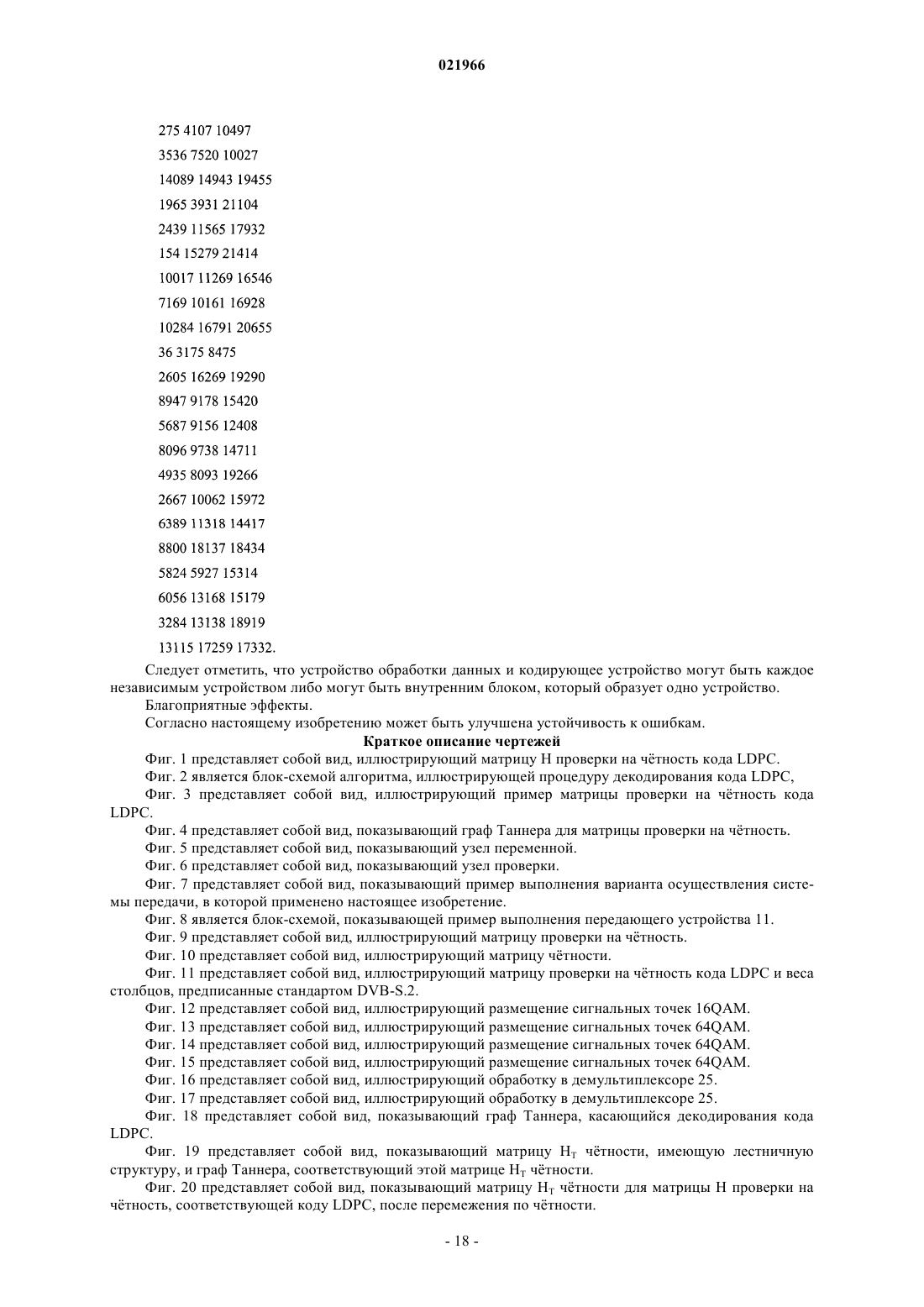

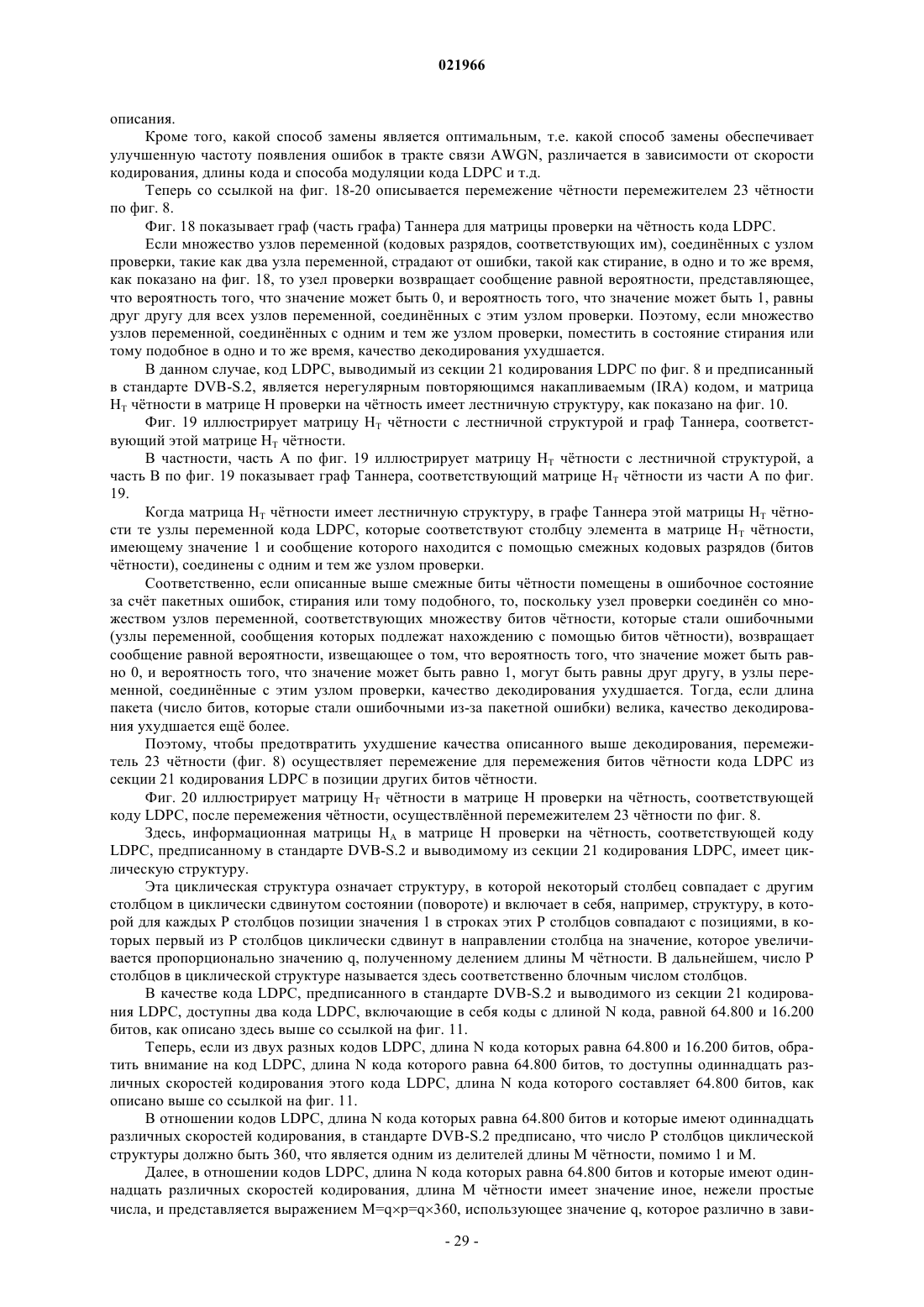

и в котором матрица проверки на четность этого кода LDPC выполнена так, что элементы со значением 1 информационной матрицы, которая соответствует длине кода матрицы проверки на четность и информационной длине, соответствующей скорости кодирования, разрешаемой по таблице начальных значений матрицы проверки на четность, представляющей положения элементов со значением 1 информационной матрицы, размещены с периодом каждых 360 столбцов в вертикальном направлении запоминающего устройства,

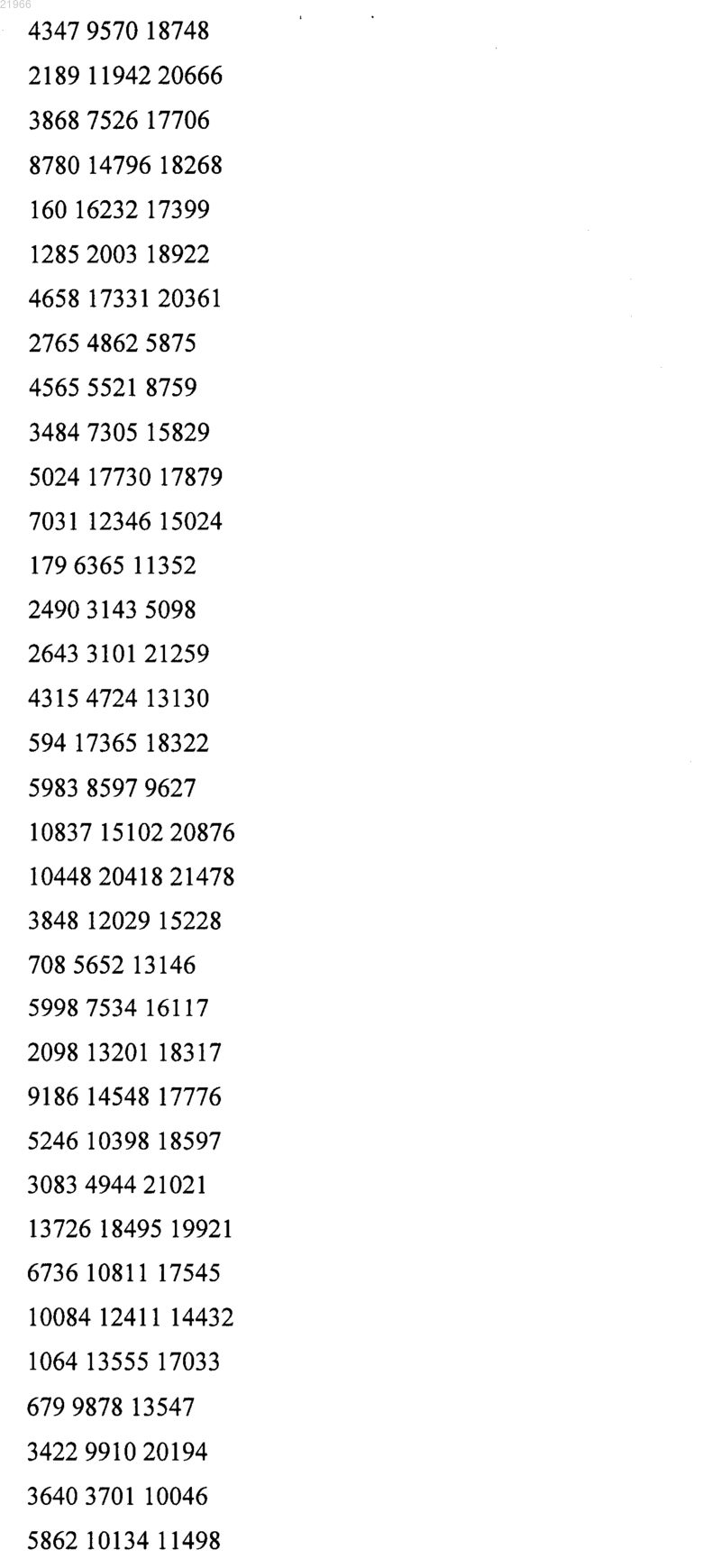

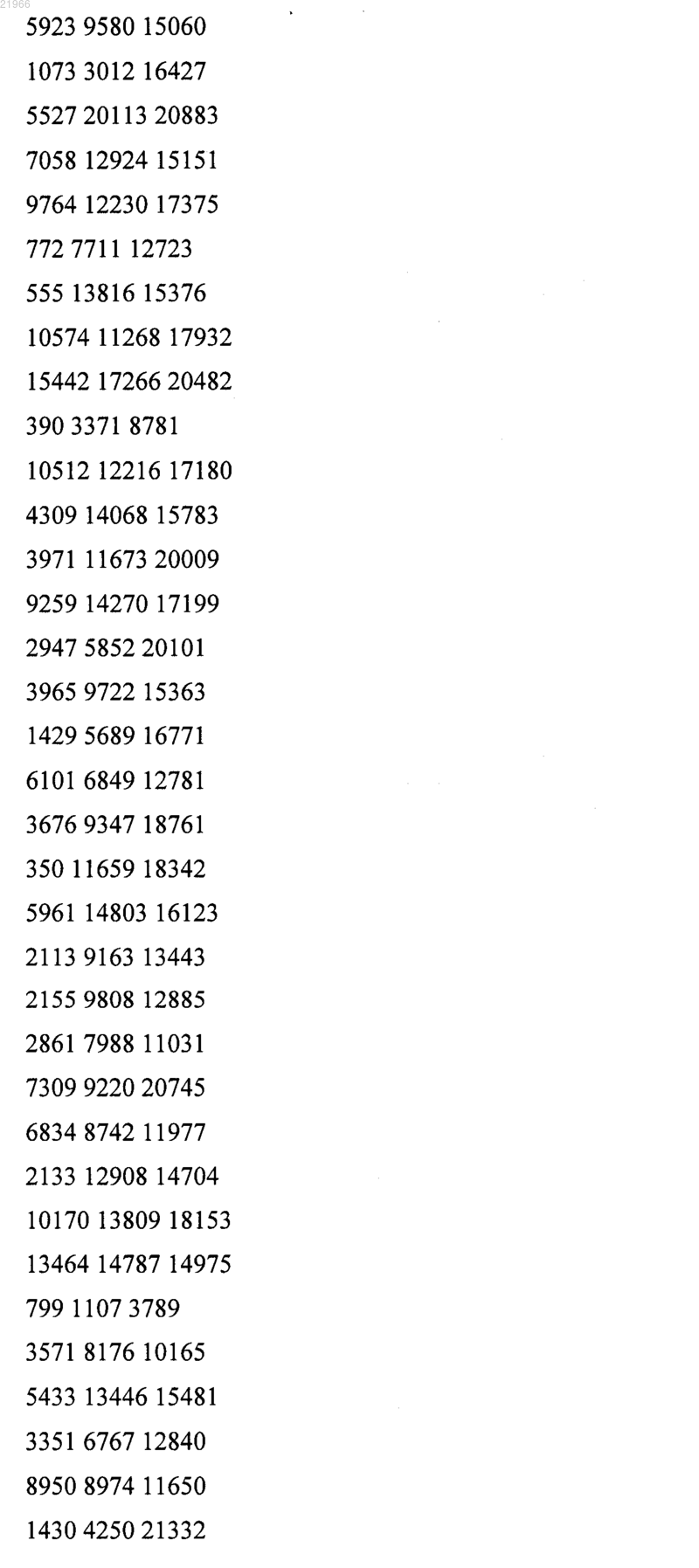

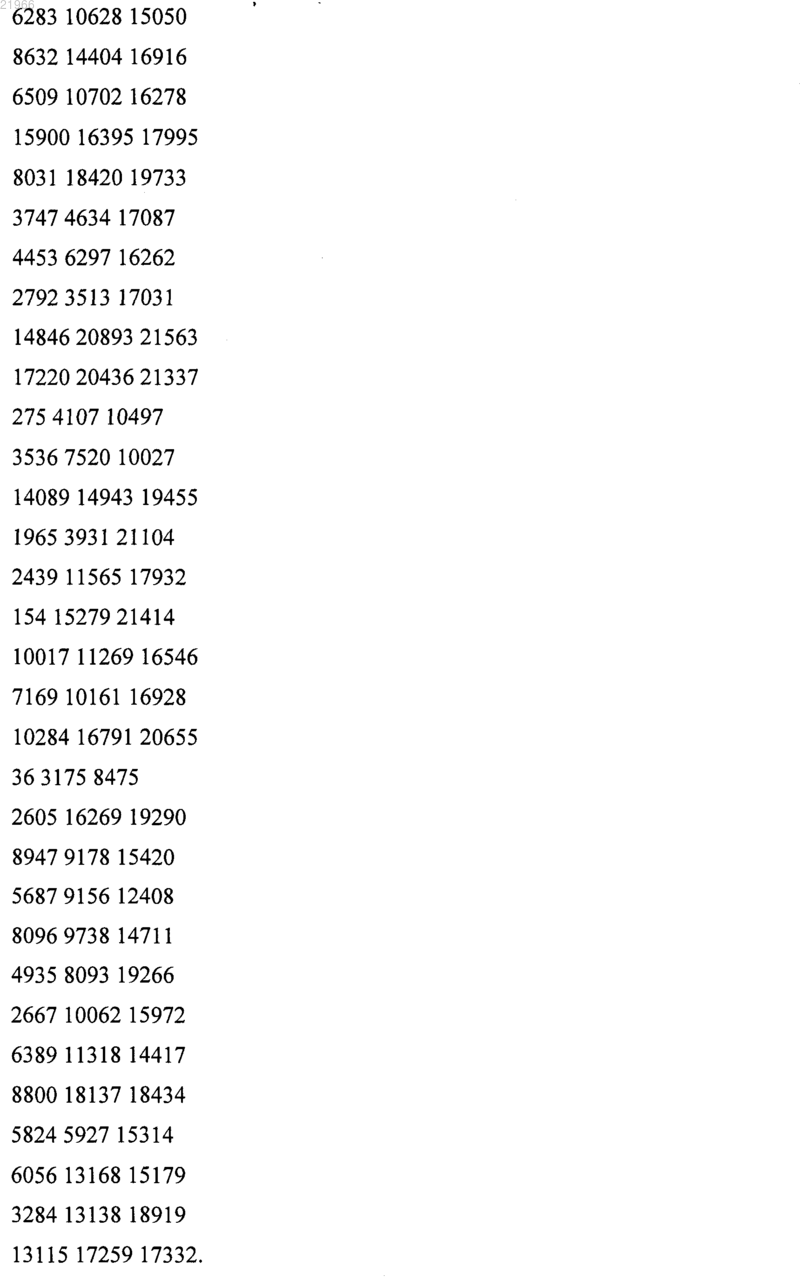

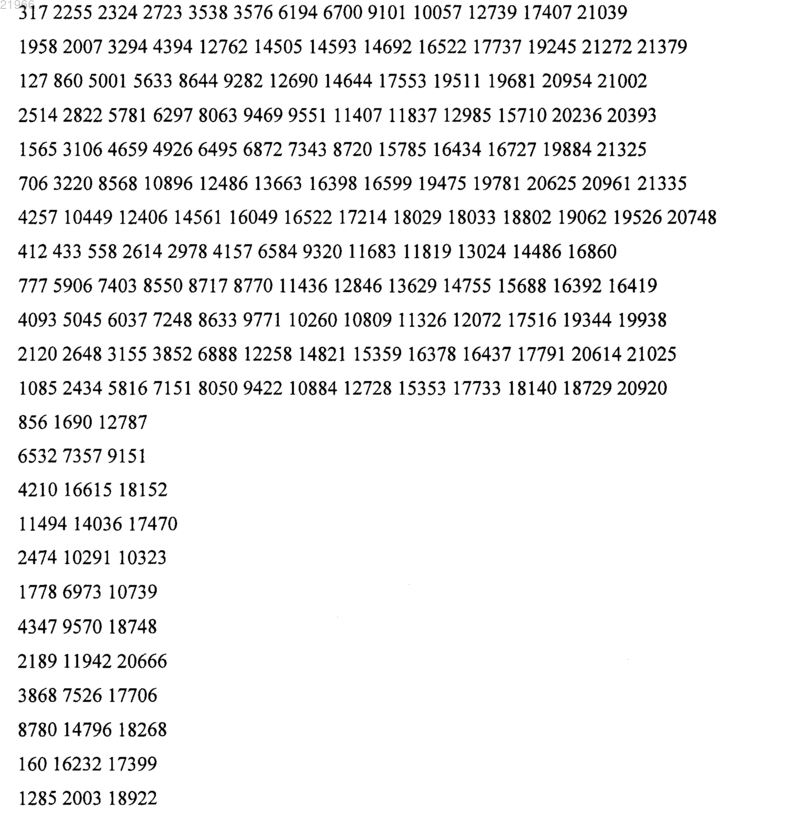

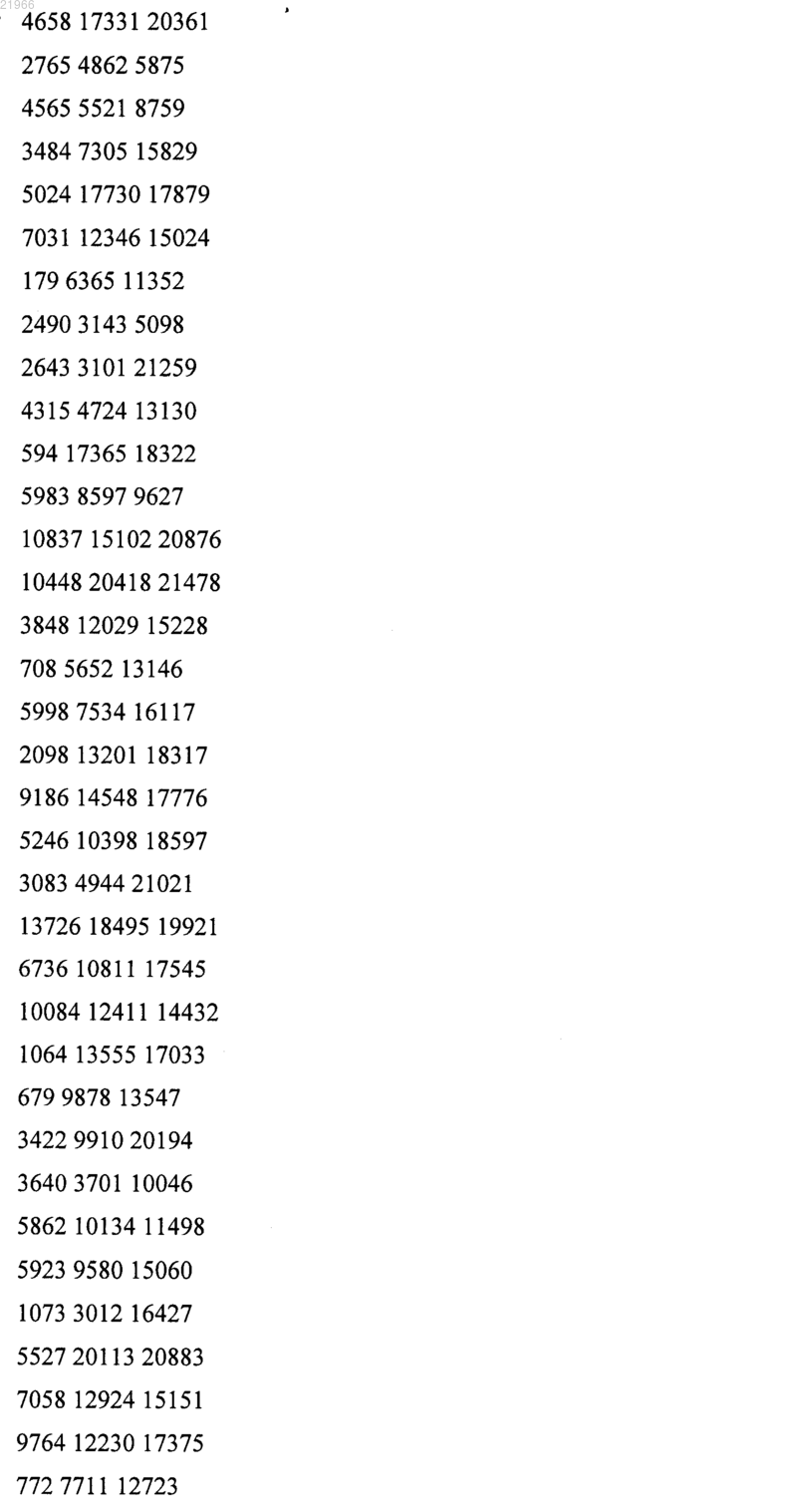

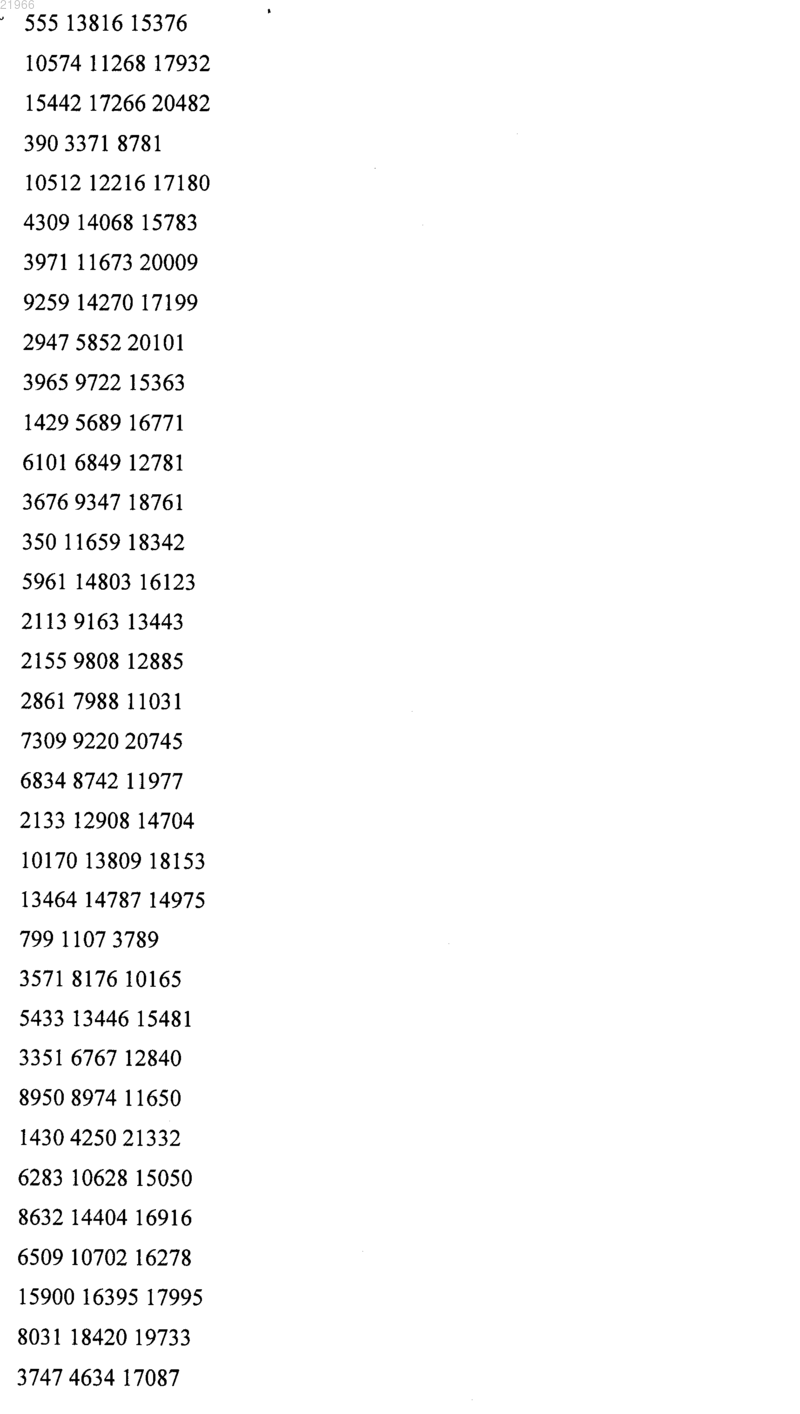

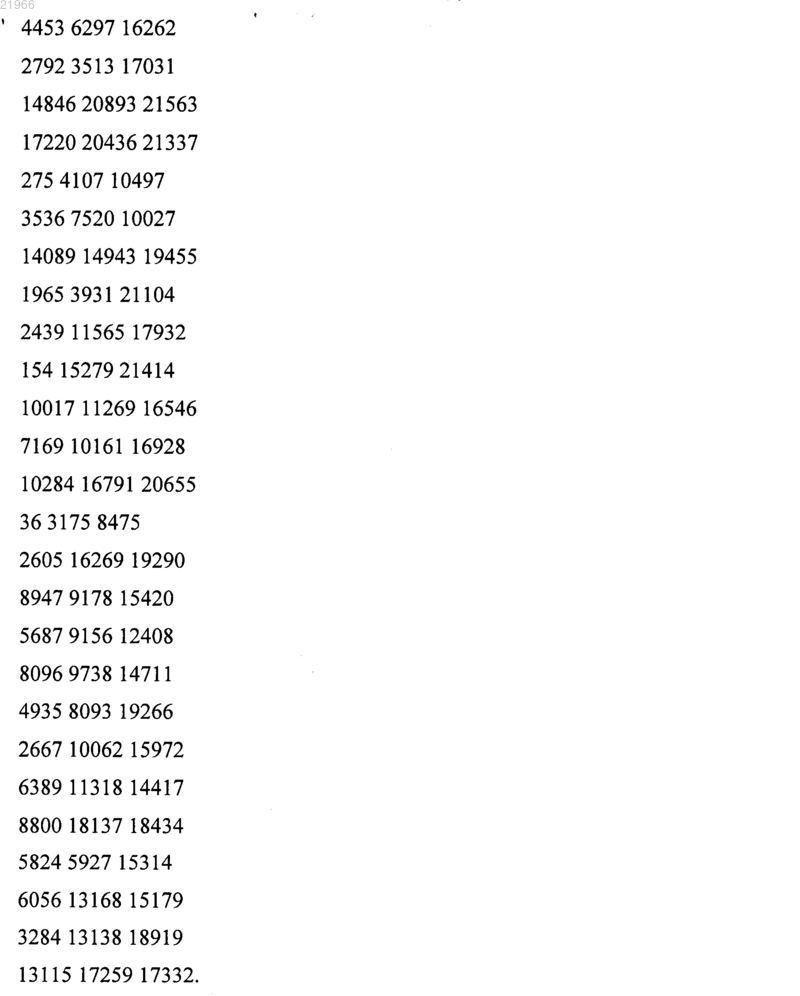

таблица начальных значений матрицы проверки на четность образована из:

2. Способ обработки данных, выполняемый устройством обработки данных по п.1, содержащий этапы, на которых

записывают кодовые биты кода LDPC (низкой плотности с контролем четности), имеющего длину кода в N битов в направлении столбца для хранения кодовых разрядов в направлении строки и в направлении столбца запоминающего устройства, имеющего емкость накопителя, требуемую для сохранения mb битов в направлении строки и сохранения N/(mb) битов в направлении столбцов;

считывают m битов из кодовых разрядов кода LDPC в направлении строки, при этом m битов кодовых битов для кода LDPC установлены как один символ и b представляет собой заданное положительное целое число; и

осуществляют замену mb кодовых битов, чтобы эти кодовые биты после замены образовали биты символов, представляющие символы, когда mb кодовых разрядов, считанных в направлении строки запоминающего средства, устанавливаются в качестве b символов;

в котором код LDPC является кодом LDPC, который имеет длину кода N, равную 64.800, и имеет скорость кодирования 2/3;

m битов равны 8 битам, тогда как целое число b равно 2;

8 кодовых битов отображаются в качестве одного символа в одну из 256 сигнальных точек, предписанных в 256QAM;

запоминающее устройство имеет 16 столбцов для хранения 8´2 битов в направлении строки и хранения 64.800/(8´2) битов в направлении столбца;

на этапе замены осуществляет замену для назначения

когда (i+1)-й бит из старшего значащего бита из 8´2 кодовых битов, считанных в направлении строки запоминающего устройства, представляется как бит bi, a (i+1)-й бит из старшего значащего бита из 8´2 битов символов двух следующих друг за другом символов представляется как бит yi;

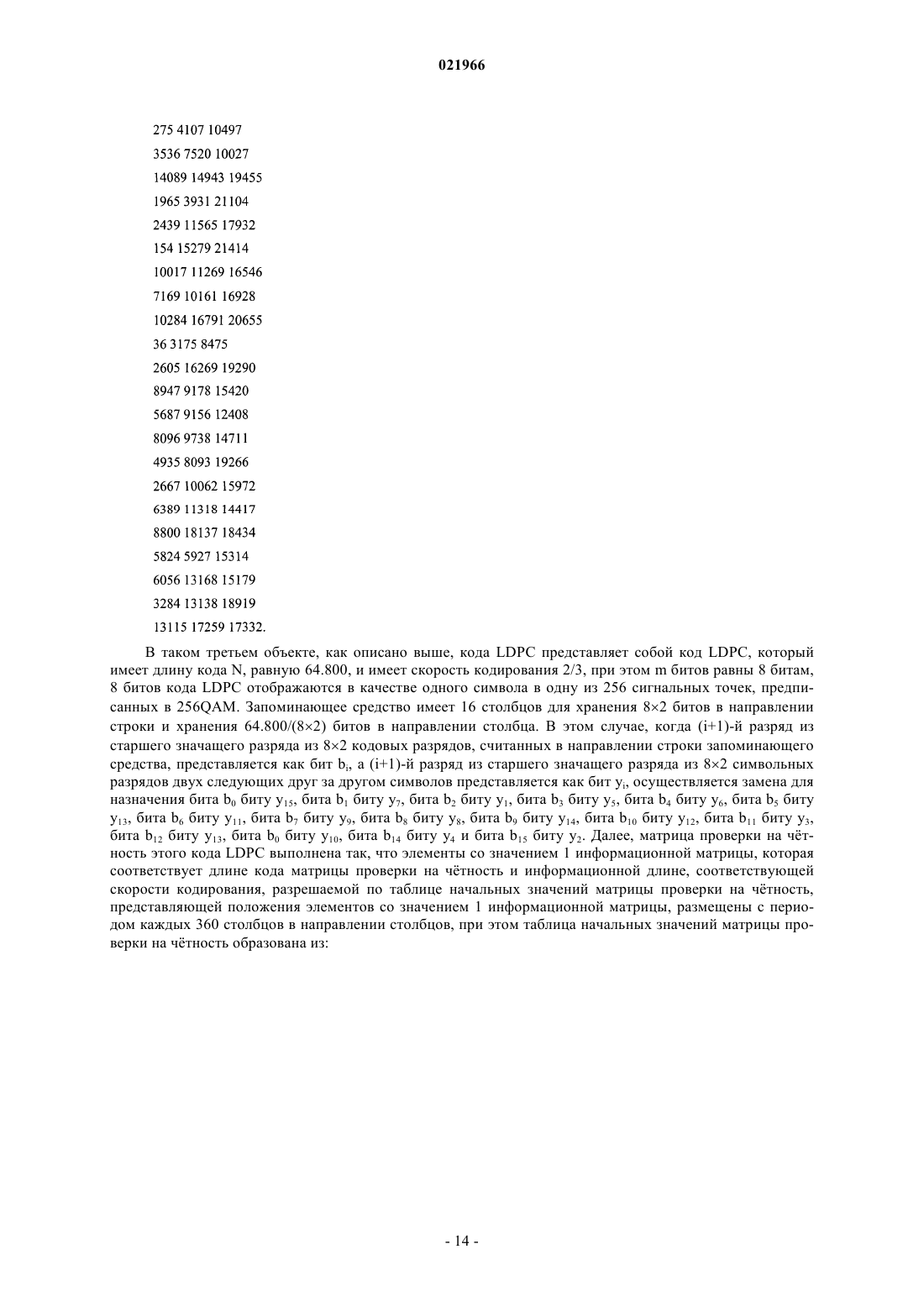

и в котором матрица проверки на четность этого кода LDPC выполнена так, что элементы со значением 1 информационной матрицы, которая соответствует длине кода матрицы проверки на четность и информационной длине, соответствующей скорости кодирования, разрешаемой по таблице начальных значений матрицы проверки на четность, представляющей положения элементов со значением 1 информационной матрицы, размещены с периодом каждых 360 столбцов в направлении столбцов,

таблица начальных значений матрицы проверки на четность образована из:

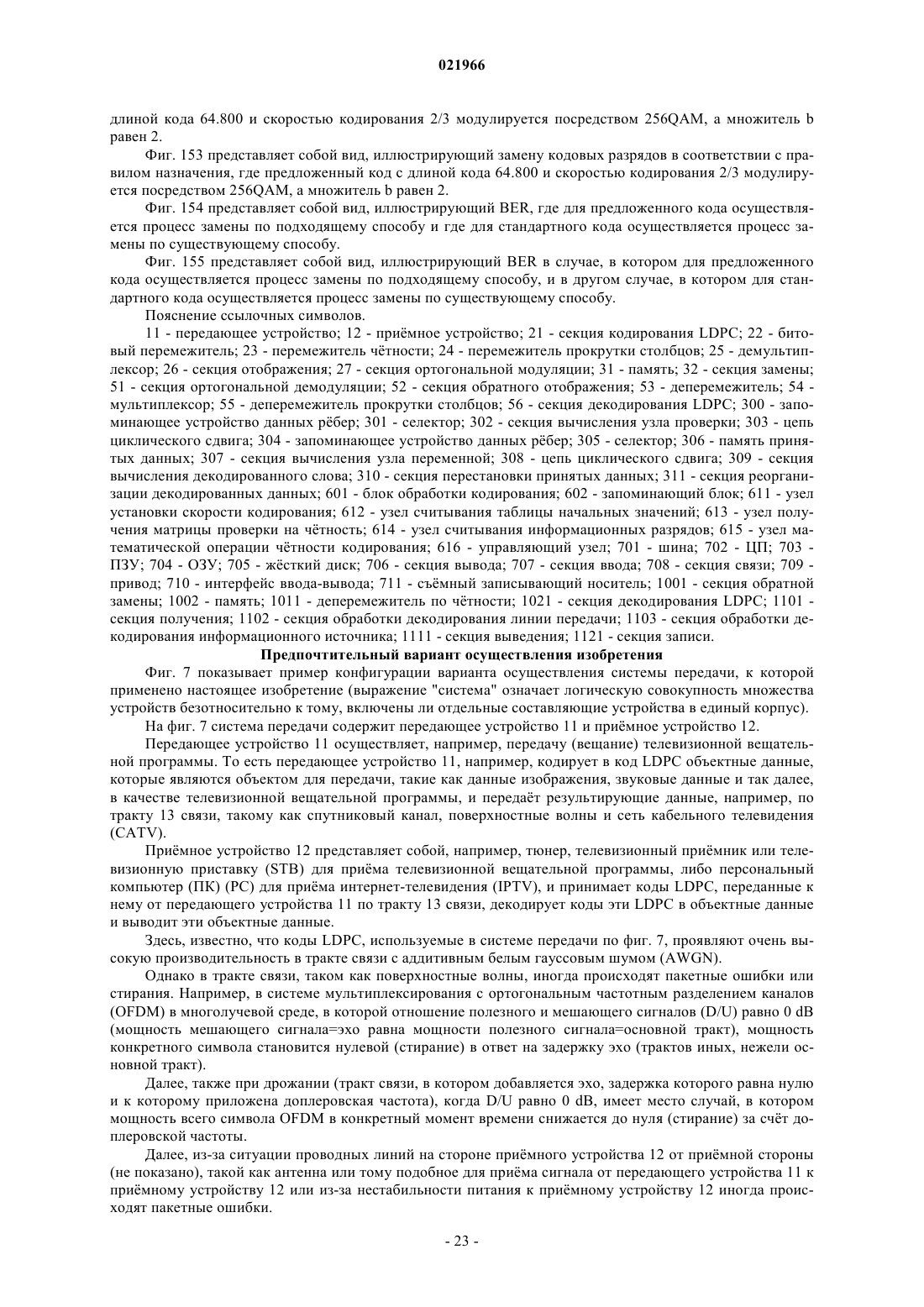

Текст