Устройство(варианты)и буферный каскад для обеспечения промежуточного преобразования и развязки источника сигнала от внешней нагрузки

Формула / Реферат

1. Устройство для промежуточного преобразования и развязки источника сигнала от внешней нагрузки, содержащее входной вывод, предназначенный для подачи на него входного сигнала от указанного источника сигнала, выходной вывод, предназначенный для формирования на нем выходного сигнала, передаваемого на указанную внешнюю нагрузку и соответствующего входному сигналу, первый источник тока смещения, предназначенный для подачи первого эмиттерного тока на первый управляющий транзистор и первого тока смещения на первый выходной транзистор, и второй источник тока смещения, предназначенный для приема второго эмиттерного тока от второго управляющего транзистора и второго тока смещения от второго выходного транзистора, причем указанный входной сигнал обеспечивает смещение указанных первого управляющего транзистора и второго управляющего транзистора, а указанный выходной вывод электрически подсоединен к эмиттеру указанного первого выходного транзистора и эмиттеру указанного второго выходного транзистора, отличающееся тем, что оно содержит источник управляющего напряжения, предназначенный для формирования управляющего напряжения и электрически включенный между эмиттером первого управляющего транзистора и эмиттером второго управляющего транзистора, при этом устройство выполнено с возможностью обеспечения изменения указанных первого тока смещения и второго тока смещения в соответствии с заранее заданной функцией от указанного управляющего напряжения.

2. Устройство по п.1, отличающееся тем, что указанный первый управляющий транзистор содержит транзистор p-n-p-типа, указанный второй управляющий транзистор содержит транзистор n-p-n-типа, указанный первый выходной транзистор содержит транзистор n-p-n-типа, и указанный второй выходной транзистор содержит транзистор p-n-p-типа.

3. Устройство по п.1, отличающееся тем, что оно содержит источники напряжения, электрически включенные между коллектором указанного первого выходного транзистора и коллектором указанного второго выходного транзистора.

4. Устройство по п.1, отличающееся тем, что указанная заранее заданная функция содержит в основном экспоненциальное отношение.

5. Устройство по п.1, отличающееся тем, что оно выполнено с возможностью прохождения через указанные первый и второй выходные транзисторы токов покоя, которые в основном не зависят от указанных первого источника тока и второго источника тока.

6. Устройство по п.1, отличающееся тем, что источник управляющего напряжения содержит резистор, транзистор p-n-p-типа, и транзистор n-p-n-типа, причем указанный резистор электрически включен между коллектором указанного транзистора p-n-p-типа и коллектором указанного транзистора n-p-n-типа, база указанного транзистора p-n-p-типа электрически соединена с указанным коллектором транзистора n-p-n-типа, база указанного транзистора n-p-n-типа электрически соединена с указанным коллектором транзистора p-n-p-типа, эмиттер указанного транзистора p-n-p-типа электрически соединен с указанным эмиттером первого управляющего транзистора, а эмиттер указанного транзистора n-p-n-типа электрически соединен с указанным эмиттером второго управляющего транзистора.

7. Устройство для промежуточного преобразования и развязки источника сигнала от внешней нагрузки, содержащее входной вывод, предназначенный для подачи на него входного сигнала от источника сигнала, и выходной вывод, предназначенный для формирования на нем выходного сигнала, передаваемого на внешнюю нагрузку, и снабженное выходным каскадом, содержащим первый транзистор n-p-n-типа с первым током покоя коллектора и первый транзистор p-n-p-типа со вторым током покоя коллектора, входным каскадом, содержащим второй транзистор p-n-p-типа, второй транзистор n-p-n-типа, первый источник тока и второй источник тока, причем эмиттер первого транзистора n-p-n-типа электрически соединен с эмиттером первого транзистора p-n-p-типа, коллектор первого транзистора n-p-n-типа соединен с первым источником напряжения, а коллектор первого транзистора p-n-p-типа соединен со вторым источником напряжения, эмиттер второго транзистора p-n-p-типа электрически соединен с первым выходным выводом источника тока и с базой первого транзистора n-p-n-типа, коллектор второго транзистора p-n-p-типа электрически соединен с указанным вторым источником напряжения, база второго транзистора p-n-p-типа электрически соединена с указанным входным выводом, а входной вывод первого источника тока электрически соединен с первым источником напряжения, эмиттер второго транзистора n-p-n-типа электрически соединен с указанным входным выводом второго источника тока и с базой указанного первого транзистора p-n-p-типа, коллектор второго транзистора n-p-n-типа, электрически соединен с указанным первым источником напряжения питания, база второго транзистора n-p-n-типа электрически соединена с указанным входным выводом, а выход второго источника тока электрически соединен с указанным вторым источником напряжения, отличающееся тем, что оно содержит источник управляющего напряжения, предназначенный для формирования управляющего напряжения и имеющий положительный вывод и отрицательный вывод, причем указанный положительный вывод электрически соединен с базой указанного первого транзистора n-p-n-типа, а указанный отрицательный вывод электрически соединен с базой указанного первого транзистора p-n-p-типа, при этом устройство выполнено с возможностью обеспечения изменения указанного первого тока покоя коллектора и указанного второго тока покоя коллектора в соответствии с заранее заданной функцией от указанного управляющего напряжения.

8. Устройство по п.7, отличающееся тем, что указанная заранее заданная функция является в основном экспоненциальной зависимостью.

9. Устройство по п.7, отличающееся тем, что указанный источник управляющего напряжения содержит резистор, третий транзистор p-n-p-типа и третий транзистор n-p-n-типа, причем указанный резистор электрически включен между коллектором указанного третьего транзистора p-n-p-типа и коллектором указанного третьего транзистора n-p-n-типа, база указанного третьего транзистора p-n-p-типа электрически соединена с указанным коллектором третьего транзистора n-p-n-типа, база указанного третьего транзистора n-p-n-типа электрически соединена с указанным коллектором третьего транзистора p-n-p-типа, эмиттер указанного третьего транзистора p-n-p-типа электрически соединен с эмиттером указанного первого управляющего транзистора, а эмиттер указанного третьего транзистора n-p-n-типа электрически соединен с указанным эмиттером второго управляющего транзистора.

10. Буферный каскад для обеспечения промежуточного преобразования и развязки источника сигнала от внешней нагрузки, содержащий входной вывод, предназначенный для подачи на него входного сигнала от источника сигнала, и выходной вывод, предназначенный для формирования на нем выходного сигнала, передаваемого на указанную внешнюю нагрузку и соответствующего входному сигналу, причем буферный каскад снабжен входной секцией, содержащей, по крайней мере, два управляющих транзистора, каждый из которых выполнен с возможностью работы с предварительно заданным током смещения, выходной секцией, содержащей, по крайней мере, два выходных транзистора, каждый из которых выполнен с возможностью работы с заранее заданным током покоя, и источником напряжения, отличающийся тем, что источник напряжения подключен к входной и выходной секциям и выполнен с возможностью формирования токов покоя, протекающих через выходные транзисторы и в основном не зависящих от величин токов смещения, протекающих через управляющие транзисторы.

11. Буферный каскад по п.10, отличающийся тем, что он выполнен с возможностью регулирования напряжения от источника напряжения таким образом, что токи смещения через два управляющих транзистора имеют разветвление в различных соотношениях.

12. Буферный каскад по п.10, отличающийся тем, что он выполнен с возможностью формирования токов покоя выходных транзисторов, в основном не зависящими от размера области эмиттера каждого из управляющих.

Текст

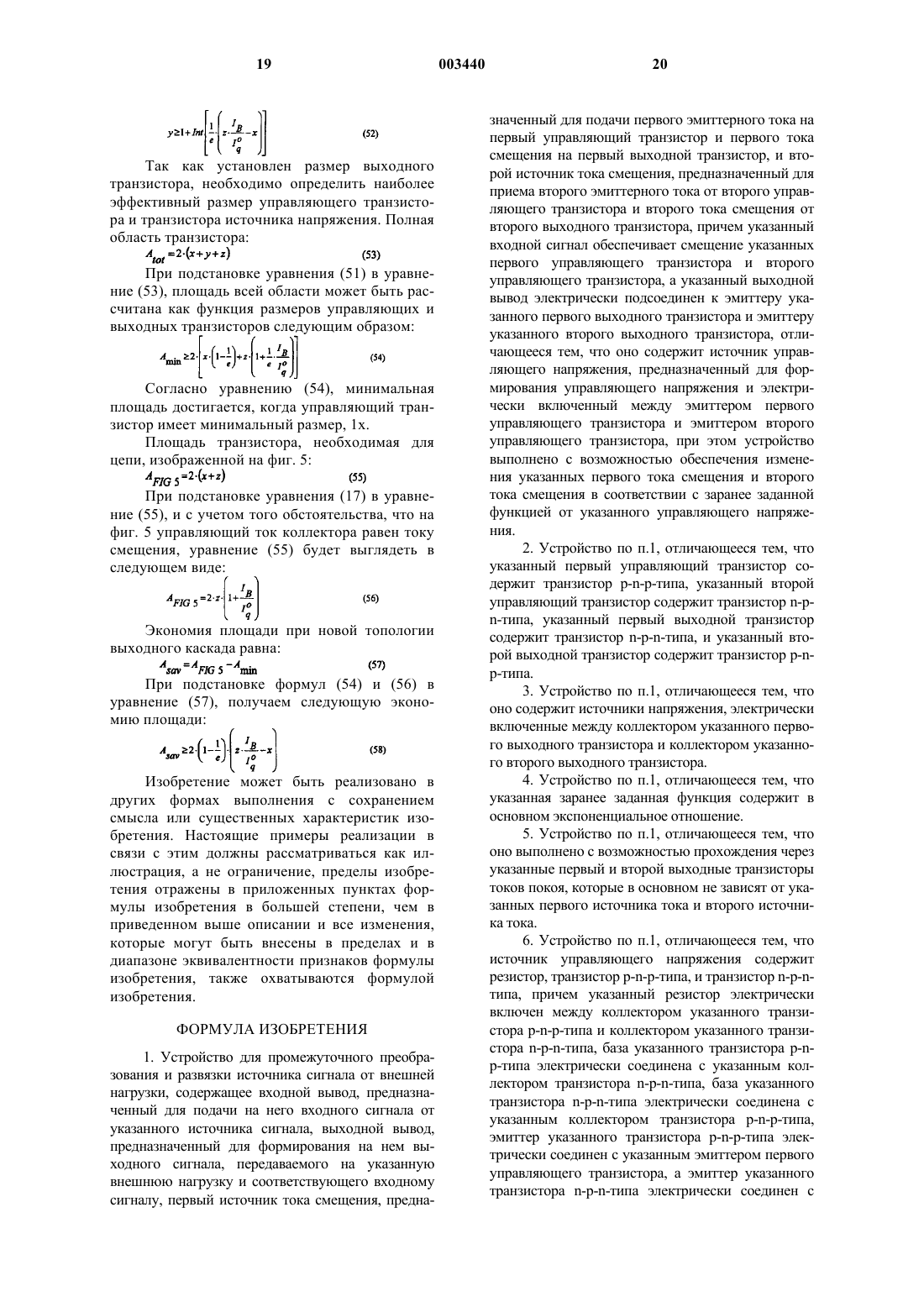

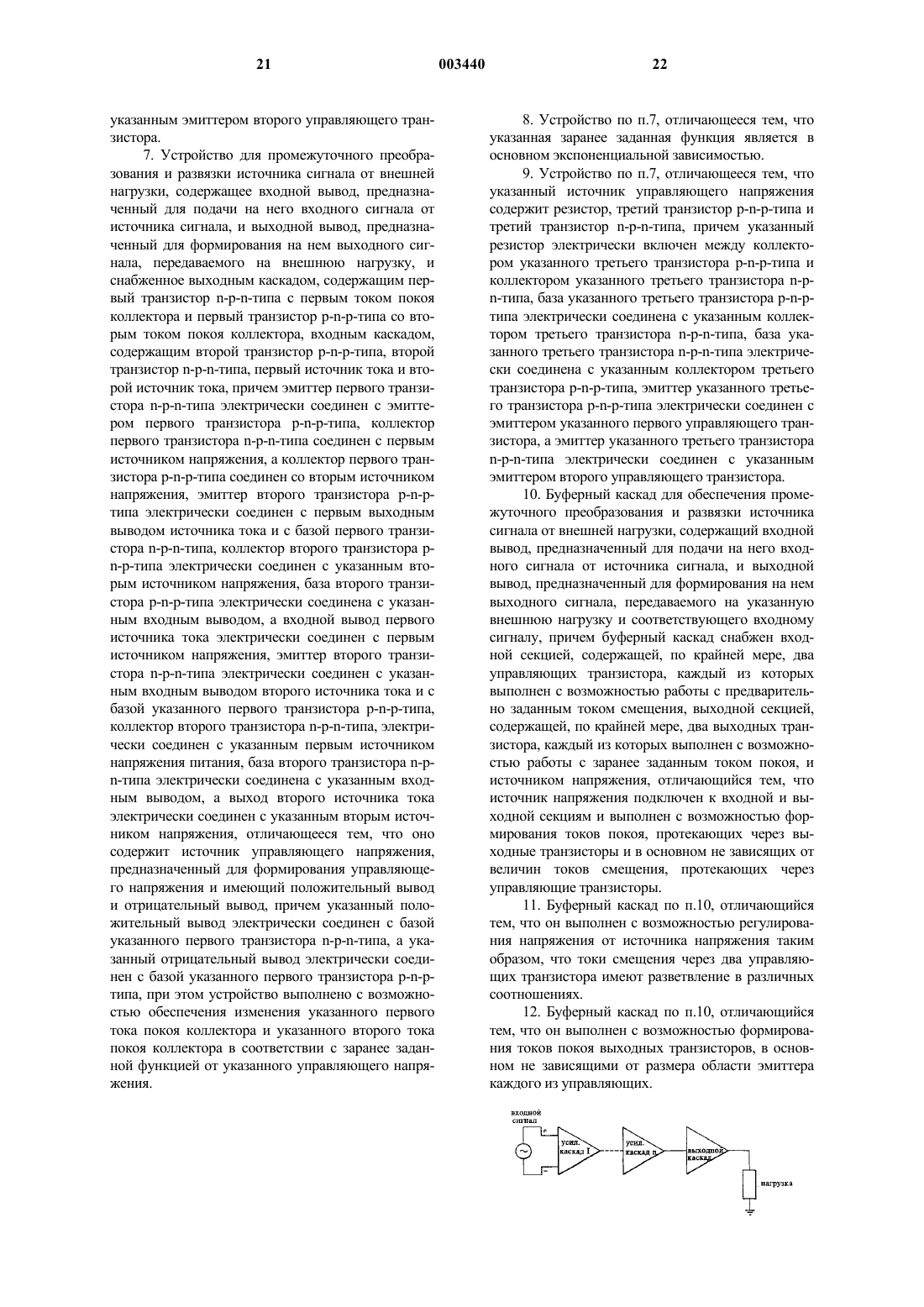

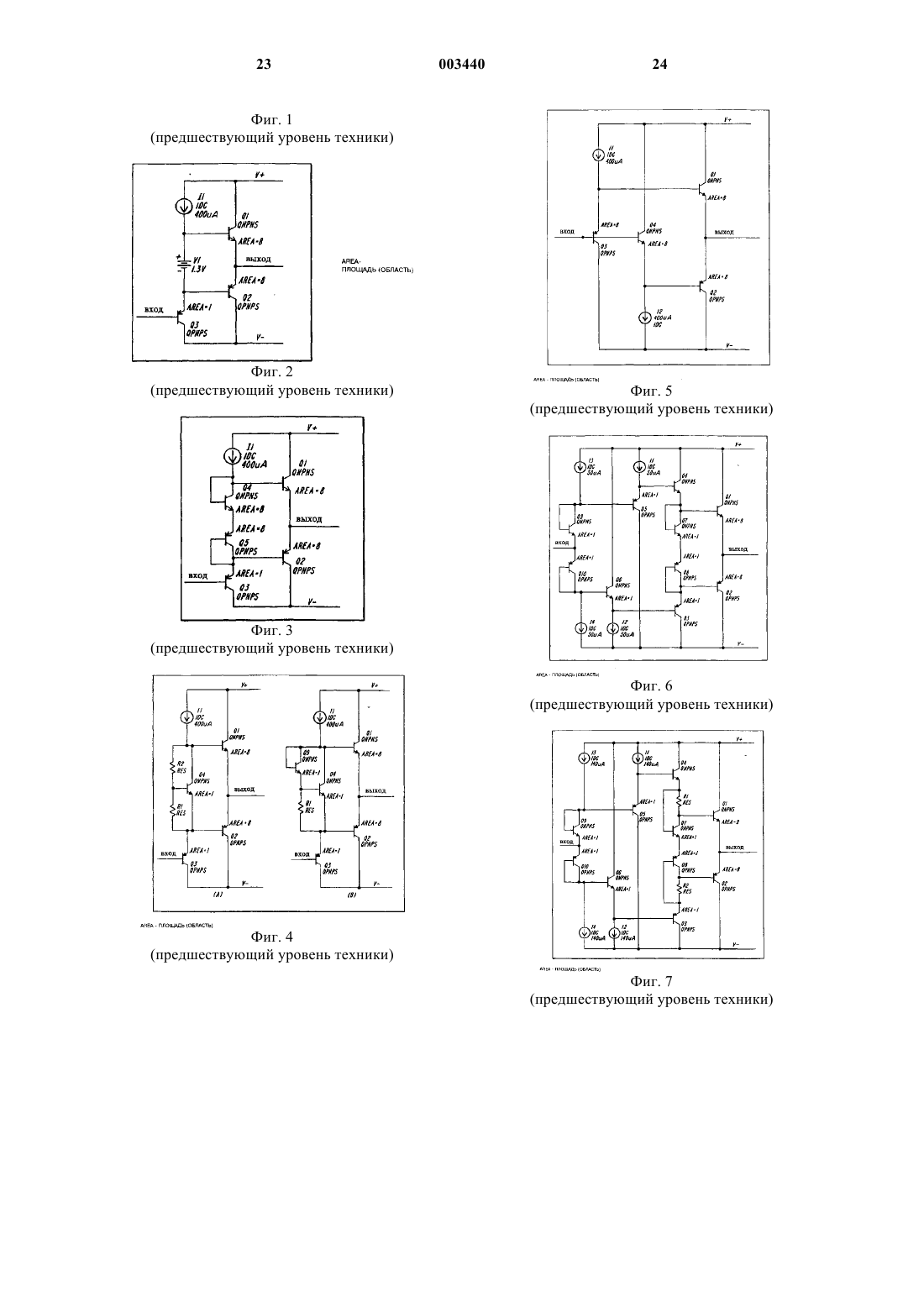

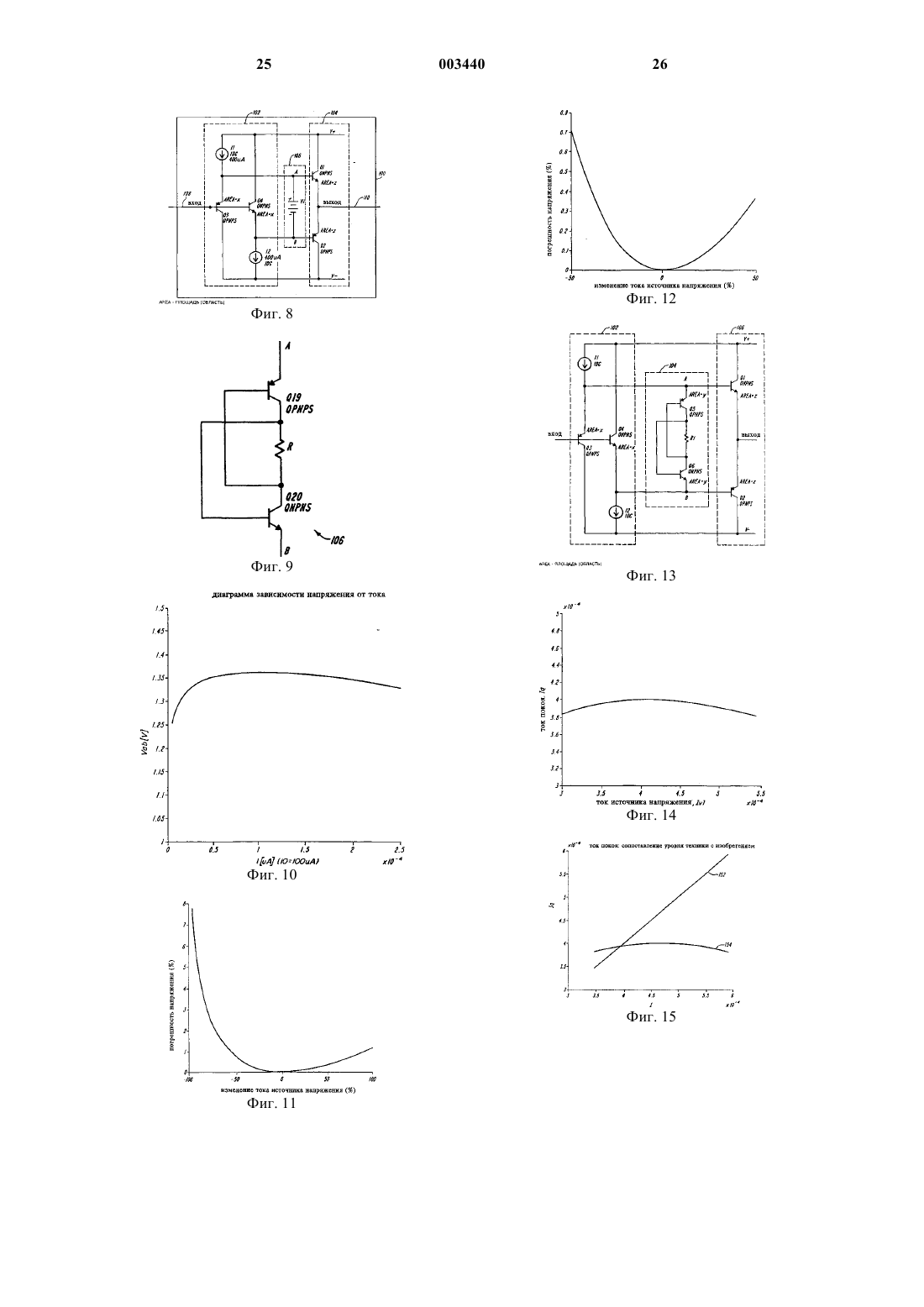

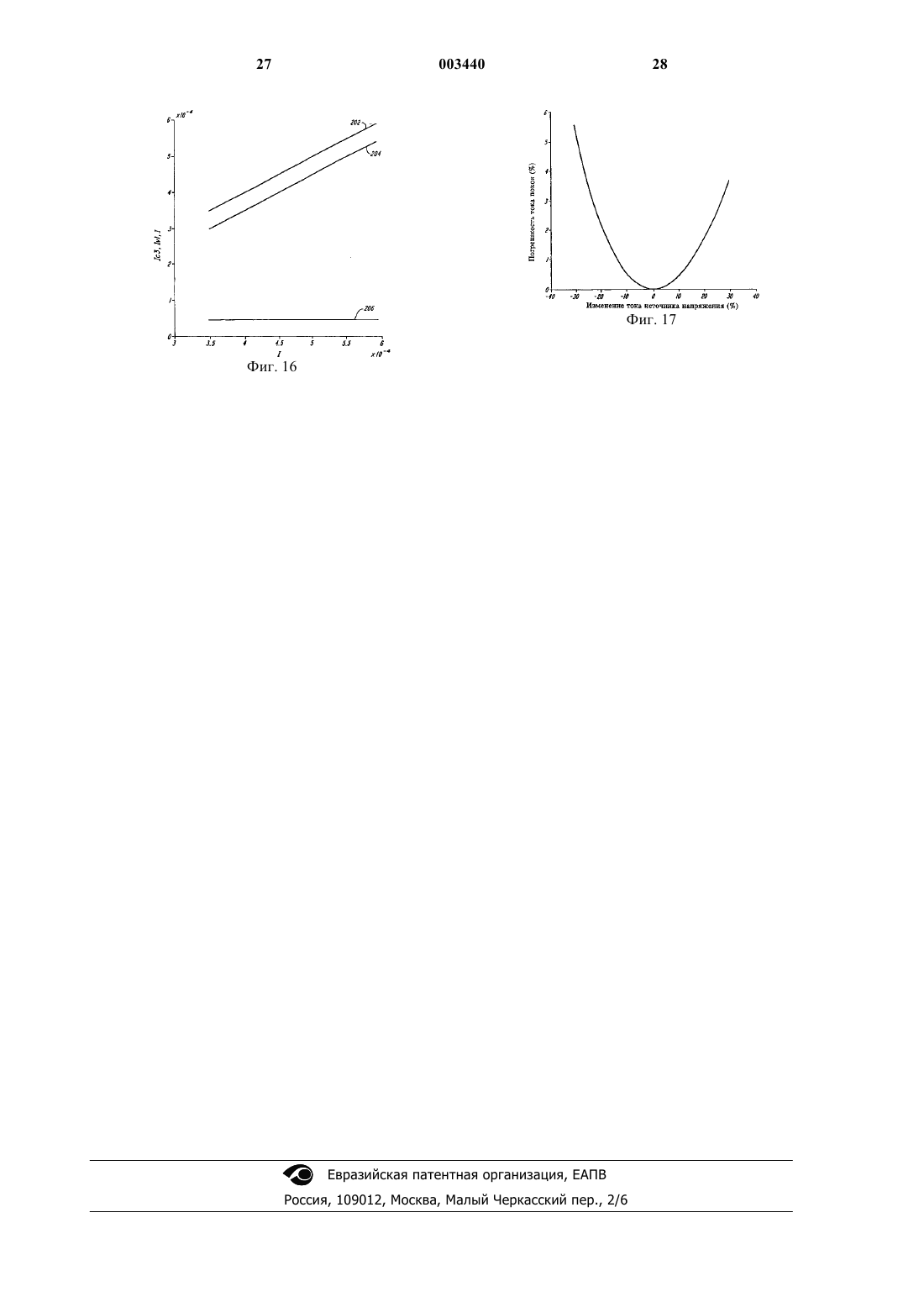

1 Область техники, к которой относится изобретение Изобретение относится к способам и устройствам, предназначенным для промежуточного преобразования и развязки источника сигнала от внешней нагрузки и, в частности, к способам и устройствам для промежуточного преобразования и развязки источника сигнала от внешней нагрузки, таким образом, что характеристики промежуточного преобразования и развязки в основном не зависят от колебаний выходного тока внешнего источника тока смещения и напряжения используемого в нем источника напряжения. Уровень техники В общем случае, представление источника сигнала зависит от параметров внешней нагрузки, соединенной с выходом источника сигнала. В том случае, когда нагрузка заведомо может проявлять различные параметры, часто требуется расположить буферное устройство между выходом источника сигнала и внешней нагрузкой. Такой буфер развязывает источник сигнала от внешней нагрузки и реализует постоянную промежуточную нагрузку, таким образом, обеспечивая устойчивую работу источника сигнала. Буфер также может обеспечивать высококачественную управляемость относительно выхода источника сигнала. Усилитель или операционный усилитель является примером источника сигналов, зависящих от нагрузки. Усилители или операционные усилители используются для усиления принятого сигнала и подачи усиленного сигнала на внешнюю нагрузку. Усилители или операционные усилители обычно содержат два или более раздельных блока или каскада,соединенных последовательно. Один из вариантов конструктивного выполнения операционного усилителя, представленный на фиг. 1, содержит n усилительных блоков и выходной каскад,где n - целое число, большее или равное единице. Из уровня техники известно несколько топологий и классов выходных каскадов. Ниже описано несколько наиболее общих топологий выходных каскадов. В общем случае, разработчики полупроводниковой техники стремятся свести к минимуму размеры кремниевой подложки, так как меньший размер подложки обеспечивает большую производительность, и позволяют получить конечный продукт меньших размеров. Таким образом, для выбора топологии схемы существенным критерием является размер общего пространства, необходимого для выполнения выходного каскада в кремнии. Для этих целей существует критерий, позволяющий сравнивать относительные размеры конкретных топологий выходных каскадов. В соответствии с этим, для обсуждения относительных размеров приведенных ниже примеров за единицу пространства выходного каскада 1 х принимается минимальный размер транзистора (который 2 обычно определяется размером эмиттера), который обычно используется в выходных каскадах. Также рассчитано, что максимальный требуемый выходной ток выходного каскада равен 16 мА. Одна из топологий выходного каскада(фиг. 2) использует комплементарный эмиттерный повторитель, в котором используются транзистор р-n-р-типа и транзистор n-р-n-типа,управляющие нагрузкой, подключенной к выходному узлу. Для этого примера рассчитано,что каждый из выходных транзисторов Q1 и Q2 занимает область размером 8 х (в восемь раз большую размера транзистора единичной геометрии), минимальный размер каждого из входных транзисторов Q3 и источника тока I1 составляет 1 х, а максимальный требуемый выходной ток равен 16 мА. Максимальный ток базы транзистора Q3 определяется величиной тока,потребляемого от источника тока I1. В этом примере где- коэффициент усиления транзистора по току. В общем случае, минимальная величинапри токе коллектора 16 мА приближенно равна 40. Для предотвращения переходных искажений, предпочтительным током покоя (током рабочей точки вольтамперной характеристики) транзисторов Q1 и Q2 является ток порядка сотен мкА, таким образом, что ток покоя приблизительно равен амплитуде тока смещения (I1),формируемого источником I1 тока. Для простоты принимается, что ток покоя равен току I1,формируемому источником тока. Для формирования тока покоя между базами транзисторовQ1 и Q2 включен источник V1 напряжения смещения. Очевидно, что, гальванический элемент не является реальным представлением источника V1 напряжения. Как показано на фиг. 3, один из вариантов выполнения источника V1 напряжения содержит два транзистора Q4 и Q5, каждый из которых включен в схему в качестве диода, имеющих ту же площадь эмиттера, что и транзисторыQ1 и Q2, обеспечивая тем самым требуемое напряжение источника V1 напряжения, показанного на фиг. 3. Пример выполнения, показанный на фиг. 3, содержит четыре больших транзистора (Q1=Q2=Q4=Q5=8x), входной транзистор(Q3=1x) и источник тока (I1=1 х), которые имеют общую площадь 34 х. Такое выполнение требует относительно большой кремниевой подложки для изготовления интегральной микросхемы. В другом примере выполнения выходного каскада, показанном на фиг. 4, источник V1 выполнен в виде усилителя напряжения, приложенного между базой и эмиттером, который занимает меньшую площадь, чем транзисторыQ4 и Q5, показанные на примере выполнения,изображенном на фиг. 3. Два общепринятых 3 варианта выполнения усилителя напряжения,приложенного между базой и эмиттером, показаны на фиг. 4(А) и 4(В). Области кремниевой подложки, занимаемые транзисторами и источниками тока для фиг. 4 А и 4 В составляют 19 х и 20 х, соответственно, что существенно меньше по сравнению с примером выполнения, изображенным на фиг. 3. Однако источники V1, изображенные на фиг. 4(А) и 4(В), содержат резисторы, величины сопротивления которых составляют десятки к, а выполнение таких резисторов требует от 6 х до 12 х кремниевой подложки. Недостатком, общим для всех вариантов выполнения выходных каскадов, изображенных на фиг. 2-4, является то, что нулевое выходное напряжение каскада, которое является нормальным состоянием покоя операционного усилителя, на который не поступает входной сигнал,соответствует приблизительно -1,3 В входного напряжения, поступающего на выходной каскад. Это необходимо для нормального смещения транзисторов Q2 и Q3. Таким образом, отрицательное выходное напряжение ограничено величиной -(V- - 1,3 В), где V- - напряжение,приложенное к отрицательной шине. Фиг. 5 иллюстрирует еще один из вариантов выполнения схемы выходного каскада, в котором преодолены ограничения по выходному напряжению, свойственные вариантам выполнения, показанным на фиг. 2-4. Однако в варианте, изображенном на фиг. 5, ограничения по выходному напряжению преодолены ценой увеличения размеров кремниевой подложки(34 х), так как все транзисторы в указанном варианте должны иметь одинаковый размер. Кроме того, вариант выполнения, изображенный на фиг. 5, требует дополнительного источника I2 тока, соответствующего источнику I1 тока, подключенному к эмиттеру транзистора Q4. Кремниевая подложка размером 34 х для схемы, изображенной на фиг. 5, может быть уменьшена до 28 х путем использования транзисторных пар, включенных по схеме Дарлингтона (составной транзистор). На фиг. 6 показана топология такой схемы, где составной транзистор Q1 - Q4 заменяет транзистор Q1, изображенный на фиг. 5, а составной транзистор Q2 Q3 заменяет транзистор Q2, изображенный на фиг. 5. Кроме того, источники тока 13 и 14 входят в состав основной части операционного усилителя, в связи с чем выходной каскад может быть уменьшен до 26 х кремниевой подложки. Вариант схемы, изображенной на фиг. 6,показан на фиг. 7, где введены два резистора в коллекторы транзисторов Q7 и Q8, которые обеспечивают формирование двух "импульсных" источников тока, в соответствии со сведениями, известными из уровня техники. Ток покоя примера выполнения, изображенного на фиг. 7, то есть ток коллекторов транзисторов Q1 и Q2, меньше зависит от соответствия и/или 4 точности источников тока I1, I2, I3 и I4. Значения сопротивлений резисторов R1 и R2 обычно малы, вследствие чего необходимая область кремниевой подложки также мала. Несмотря на то, что источники тока включены последовательно, значения сопротивлений, которым должны соответствовать резисторы R1 и R2,относительно малы. Преимущество использования транзистора, соответствующего схеме Дарлингтона в примерах выполнения, изображенных на фиг. 6 и 7, заключается в добавлении третьего уровня промежуточного преобразования, по сравнению со схемой, изображенной на фиг. 5, которая обеспечивает только два уровня промежуточного преобразования. Этот третий уровень промежуточного преобразования существенно повышает уровень развязки усилителя от внешней нагрузки. Однако, примеры выполнения, показанные на фиг. 6 и 7, повышают уровень развязки за счет снижения максимальной амплитуды напряжения, формируемого на выходе буферного каскада. В то время как выходное напряжение схемы, изображенной на фиг. 5, находится в пределах +/-(Vпитания -0,85 В), выходное напряжение схемы, изображенной на фиг. 6, находится в пределах всего +/(Vпитания -1,5 V), где Vпитания = V + = V-. В действительности, выходное напряжение схемы,изображенной на фиг. 7, может быть даже меньшим из-за дополнительного падения напряжения на резисторах R1 и R2. В патенте США 5,323,122 Бауэрса описывается буферный усилитель, имеющий первый источник тока смещения и второй источник тока смещения. Но, в отличие от заявляемого изобретения, напряжение на резисторе Rs изменяется прямо пропорционально силе тока, проходящего через резистор, и при этом не имеется источника управляющего напряжения, который поддерживал бы постоянное напряжение при изменении силы тока, который через него проходит. Сущность изобретения Настоящее изобретение относится к устройствам для промежуточного преобразования и обеспечения развязки источника сигнала от внешней нагрузки. Устройство выполнено в виде выходного каскада, сходного по схеме с выходным каскадом, изображенным на фиг. 5,но занимающего меньшую площадь. В соответствии с одним аспектом изобретения, буферный каскад предназначен для промежуточного преобразования и развязки источника сигнала от внешней нагрузки. Каскад, имеющий входной вывод, предназначенный для подачи на него входного сигнала от указанного источника сигнала и выходной вывод, предназначенный для формирования на нем выходного сигнала, соответствующего указанному входному сигналу,подаваемого на внешнюю нагрузку, содержит: входную секцию, включающую, по крайней мере, два управляющих транзистора, каж 5 дый из которых предназначен для работы с заранее заданным током смещения; выходную секцию, содержащую, по крайней мере, два выходных транзистора, каждый из которых предназначен для работы с заранее заданным током покоя; и источник напряжения, соединенный с входной и выходной секциями, выполненный с возможностью формирования тока покоя, протекающего через выходные транзисторы, не зависящего от величины тока смещения, протекающего через управляющие транзисторы. В одном из вариантов выполнения подача напряжения, формируемого источником напряжения, вызывает ток смещения, протекающий через два управляющих транзистора, разветвленный неравномерно между первым контуром,содержащим источник напряжения и один управляющий транзистор и вторым контуром,содержащим источник напряжения и другой управляющий транзистор. Еще в одном из вариантов выполнения ток покоя в основном не зависит от размера области эмиттера каждого из управляющих транзисторов в том случае, если площадь эмиттера каждого из управляющих транзисторов меньше чем площадь эмиттера каждого из выходных транзисторов. Еще в одном из вариантов выполнения в процессе работы сумма напряжений базаэмиттер выходных транзисторов равна сумме напряжений база-эмиттер управляющих транзисторов. И еще в одном из вариантов выполнения через источник напряжения протекает ток, равный разности между током смещения и током коллектора каждого из управляющих транзисторов. Еще в одном из вариантов выполнения базы управляющих транзисторов, соединенные между собой, используются в качестве входного вывода промежуточного каскада. Еще в одном из вариантов выполнения эмиттеры выходных транзисторов, соединенные между собой, используются в качестве выходного вывода промежуточного каскада. Еще в одном из вариантов выполнения каскад дополнительно содержит источник тока,предназначенный для формирования тока смещения для каждого из управляющих транзисторов. Еще в одном из вариантов выполнения эмиттер каждого из управляющих транзисторов подключен к источнику тока таким образом,что, по крайней мере, часть тока смещения протекает через управляющий транзистор. Еще в одном из вариантов выполнения источник напряжения включен между эмиттерами управляющих транзисторов и между базами выходных транзисторов. Еще в одном из вариантов выполнения выходные транзисторы выполнены противоположного типа проводимости. 6 Еще в одном из вариантов выполнения источник напряжения содержит два транзистора источника напряжения противоположного типа проводимости и резистор, включенный между коллектором первого из транзисторов источника напряжения и базой другого транзистора источника напряжения, и между коллектором другого транзистора источника напряжения и базой первого из транзисторов источника напряжения. Еще в одном из вариантов выполнения,токи смещения, протекающие через управляющие транзисторы, равны. В соответствии с еще одним аспектом изобретения, все токи выходного каскада в основном не зависят от токов источников тока смещения и управляются одним источником, например, источником напряжения. В одном из предпочтительных вариантов выполнения, источник напряжения управляется одним резистивным элементом, и, в конечном счете, все токи в выходном каскаде управляются тем же самым резистивным элементом. Еще в одном из предпочтительных вариантов выполнения источник напряжения, формирующий все токи, выполнен в виде двухполюсника, первый вывод которого включен между выходом первого из управляющих транзисторов и входом первого из выходных транзисторов, а второй вывод включен между выходом другого управляющего транзистора и входом другого выходного транзистора. В соответствии с другим аспектом, устройство содержит входной вывод, предназначенный для подачи на него входного сигнала от источника сигнала, и выходной вывод, предназначенный для формирования на нем выходного сигнала, соответствующего входному сигналу,подающегося на внешнюю нагрузку. Устройство содержит два источника тока, два управляющих транзистора, два выходных транзистора и источник управляющего напряжения. Первый источник тока одновременно подает ток эмиттера на первый управляющий транзистор и ток смещения на первый выходной транзистор. Второй источник тока одновременно принимает ток эмиттера со второго управляющего транзистора и ток базы со второго выходного транзистора. Входной сигнал обеспечивает смещение,как первого управляющего транзистора, так и второго управляющего транзистора. Выходной вывод электрически соединен с эмиттером первого выходного транзистора и эмиттером второго выходного транзистора. Источник управляющего напряжения электрически включен между эмиттером первого управляющего транзистора и эмиттером второго управляющего транзистора. Ток через источник напряжения изменяется в соответствии с предварительно заданной функцией от управляющего напряжения, такой,что ток покоя выходных транзисторов остается практически не зависящим от любых парамет 7 рических изменений, вносимых источником входного тока и/или управляющими транзисторами. В соответствии с одним предпочтительным вариантом выполнения изобретения, первый управляющий транзистор содержит транзистор р-n-р-типа, второй управляющий транзистор содержит транзистор n-р-n-типа, первый выходной транзистор содержит транзистор n-рn-типа, и второй выходной транзистор содержит транзистор р-n-р-типа. В другом примере выполнения изобретения, источник напряжения электрически включен между коллектором первого выходного транзистора и коллектором второго выходного транзистора. Еще в одном примере выполнения предварительно определенная функция является в основном экспоненциальным отношением. Еще в одном примере выполнения источник управляющего напряжения содержит резистор, транзистор р-n-р-типа и транзистор n-р-nтипа. В этом примере реализации резистор электрически включен между коллектором транзистора р-n-р-типа и коллектором транзистора n-рn-типа. База транзистора р-n-р-типа электрически соединена с коллектором транзистора n-р-nтипа, база n-р-n-транзистора электрически соединена с коллектором транзистора р-n-р-типа,эмиттер транзистора р-n-р-типа электрически соединен с эмиттером первого управляющего транзистора, и эмиттер транзистора n-р-n-типа электрически соединен с эмиттером второго управляющего транзистора. Перечень фигур чертежей Первый и последующие объекты этого изобретения и их различные отличительные особенности могут быть более полно поняты из приведенного ниже описания с сопровождающими фигурами, где фиг. 1 иллюстрирует схематическое представление типичного операционного усилителя,известного из уровня техники; фиг. 2 - схематическое представление известной из уровня техники архитектуры эмиттерного повторителя выходного каскада; фиг. 3 - схематическое представление известной из уровня техники архитектуры выходного каскада, имеющего общий для двух транзисторов источник напряжения смещения; фиг. 4(А) - схематическое представление известной из уровня техники архитектуры базаэмиттерного умножителя выходного каскада; фиг. 4(В) - схематическое представление известной из уровня техники архитектуры другого база-эмиттерного умножителя выходного каскада; фиг. 5 - схематическое представление известной из уровня техники архитектуры другого примера выполнения выходного каскада; фиг. 6 - схематическое представление известной из уровня техники архитектуры вариан 003440 8 та выполнения выходного каскада, изображенного на фиг. 5; фиг. 7 - схематическое представление известной из уровня техники архитектуры еще одного варианта выполнения выходного каскада, изображенного на фиг. 5; фиг. 8 - схематическое представление архитектуры усовершенствованного выходного каскада, в соответствии с настоящим изобретением; фиг. 9 - схематическое представление предпочтительного варианта выполнения источника 106 управляющего напряжения, изображенного на фиг. 8; фиг. 10 - графическое представление напряжения через источник управляющего напряжения, показанный на фиг. 9; фиг. 11 - графическое представление погрешности напряжения источника управляющего напряжения, изображенного на фиг. 9, при изменении тока на 50%; фиг. 12 - погрешность напряжения источника управляющего напряжения, изображенного на фиг. 9, при изменении тока на 100%; фиг. 13 - схематическое представление выходного каскада, изображенного на фиг. 8, выполненного содержащим источник управляющего напряжения, изображенный на фиг. 9; фиг. 14 - графическое представление тока покоя выходных транзисторов, изображенных на фиг. 13, как функции тока через источник напряжения; фиг. 15 - графическое представление тока покоя в соответствии с током смещения выходных транзисторов, изображенных на фиг. 13; фиг. 16 - диаграммы выходного тока источника тока смещения, тока источника управляющего напряжения и тока через управляющий транзистор, направленного против выхода источника тока смещения; и фиг. 17 графически иллюстрирует процент ошибки тока покоя в соответствии с процентным изменением тока через источник управляющего напряжения. Сведения, подтверждающие возможность осуществления изобретения Настоящее изобретение относится к усовершенствованному выходному каскаду, предназначенному для обеспечения развязки между источником сигнала и внешней нагрузкой. Один из предпочтительных вариантов выполнения выходного каскада 100, показанный в схематическом виде на фиг. 8, содержит входную секцию 102, выходную секцию 104 и источник 106 управляющего напряжения. Входная секция 102 принимает входной сигнал от источника сигнала (не показан) и управляет работой выходной секции 104 в зависимости от входного сигнала. Выходная секция 104 обеспечивает высокую нагрузочную способность сигнала управления внешней нагрузкой (не показана), и как будет показано в дальнейшем, источник управляюще 9 го напряжения 106 - элемент общий для входной секции 102 и выходной секции 104. В соответствии с одним аспектом настоящего изобретения, источник управляющего напряжения 106 устанавливает фиксированные суммы напряжения базы-эмиттера, как для входной секции 102,так и для выходной секции 104, и обеспечивает общий путь для тока, определяемого как разница между током смещения и током коллектора управляющих транзисторов Q3 и Q4 входной секции 102. Входная секция 102 включает биполярный транзистор Q3 р-n-р-типа и биполярный транзистор Q4 n-р-n-типа, первый источник тока I1 и второй источник тока I2. Базы транзисторов Q3 и Q4 электрически соединены вместе и подключены к входному выводу 108 для подачи на них входного сигнала. Эмиттер транзистора Q3 электрически соединен с выходом первого источника тока I1, коллектор транзистора Q3 электрически соединен с отрицательной шиной напряжения, то есть, с первым источником напряжения V-, а вход первого источника тока электрически соединен с положительной шиной напряжения, то есть, с вторым источником напряжения V+. Коллектор транзистора Q4 электрически соединен со вторым источником напряжения V+, эмиттер транзистора Q4 электрически соединен с выходом второго источника тока I2, и выход второго источника тока I2 электрически соединен с первым источником напряжения V-. Выходная секция 104 каскада 100 содержит биполярный транзистор Q1 n-р-n-типа и биполярный транзистор Q2 р-n-р-типа. Эмиттеры транзисторов Q1 и Q2 электрически соединены вместе и подключены к выходному выводу 110, предназначенному для подачи выходного сигнала на внешнюю нагрузку. Коллектор транзистора Q1 электрически соединен со вторым источником напряжения V+, а коллектор транзистора Q2 электрически соединен с первым источником напряжения V-. База транзистора Q1 электрически соединена с выходом первого источника тока I1 и эмиттером транзистора Q3. База транзистора Q2 электрически соединена с входом второго источника тока I2 и эмиттером транзистора Q4. Иcтoчник yпpaвляющeгo напряжения 106 содержит положительный вывод и отрицательный вывод. Положительный вывод источника 106 электрически соединен с базой транзистораQ1, эмиттером транзистора Q3 и выходом первого источника тока I1. Отрицательный вывод источника 106 электрически соединен с базой транзистора Q2, эмиттером транзистора Q4 и входом второго источника тока I2. В соответствии с одним аспектом изобретения, напряжение V1 через источник управляющего напряжения 106 установлено таким,что желательный ток покоя течет через выходные транзисторы Q1 и Q2. Регулировка напря 003440 10 жения V1 заставляет токи смещения I1 и I2 распределяться в различных отношениях между цепью, содержащей транзистор Q3 и источник 106, и цепью, содержащей транзистор Q4 и источник 106, соответственно. В большой и существенной степени все токи выходного каскада 100 независимы от источников тока I1 и I2 и могут управляться напряжением V1 на источнике управляющего напряжения 106. Также, разветвление тока между цепью, включающей транзистор Q3 и источник 106, и цепью, включающей транзистор Q4 и источник 106, может управляться путем изменения области эмиттера каждого из транзисторов Q3 и Q4. Изменение размера каждого из транзисторов Q3 и Q4 и/или изменение токов источников тока I1 и/или I2 не влияет на ток покоя транзисторов Q1 и Q2. Это фундаментальное различие между настоящим изобретением и вариантом выполнения, известным из уровня техники, показанным на фиг. 5. Таким образом, в варианте выполнения, показанном на фиг. 8, площадь эмиттера каждого из управляющих транзисторов Q3 и Q4 произвольна и не зависит от площади эмиттера каждого из выходных транзисторов Q1 и Q2, до тех пор,пока площадь эмиттера каждого из управляющих транзисторов Q3 и Q4 меньше, чем площадь эмиттера каждого из выходных транзисторов Q1 и Q2, что обеспечивает существенную свободу проектирования. Если площади эмиттера управляющих транзисторов Q3 и Q4 меньше,чем площади эмиттера выходных транзисторовQ1 и Q2, токи коллектора Q3 и Q4 - меньше,чем соответствующие токи в цепи, показанной на фиг. 5. Дополнительный ток течет через источник управляющего напряжения 106. Так как площадь эмиттера относится непосредственно к площади кремниевой подложки, в изобретении используется относительно меньшая площадь кремниевой подложки, чем это имело место в цепи, известной из предшествующего уровня техники, показанной на фиг. 5. Приведенные ниже рассуждения даны для детального описания действия выходного каскада 100:IV1 - ток через источник напряжения V1;ISP - ток насыщения транзистора р-n-ртипа;VT - тепловое напряжение, 25.9 mV;- коэффициент усиления транзистора по току; х - площадь эмиттера каждого из управляющих транзисторов Q3 и Q4; и z - площадь эмиттера каждого из выходных транзисторов Q1 и Q2. Вообще, токи коллектора всех транзисторов Q1, Q2, Q3 и Q4 могут быть выражены как 12 Ток коллектора управляющих транзисторов Q3 и Q4 может быть рассчитан как функция управляющего источника напряжения смещения 106. Сумма напряжений базы-эмиттера транзисторов Q3 и Q4 равна V1, как показано в уравнении (11). где z - площадь эмиттера каждого из транзисторов Q1 и Q2,х - площадь эмиттера каждого из транзисторов Q3 и Q4, и Уравнение (11) может быть изменено путем подстановки значений напряжений базыэмиттера транзисторов Q3 и Q4 из уравнений (4) и (5), следующим образом: Сумма напряжений базы-эмиттера выходных транзисторов Q1 и Q2 равна напряжению источника напряжения V1 Для большинства применений токи источников тока смещения I1 и I2 равны. Случай,когда токи источников тока смещения не равны,рассматривается как эффект второго порядка и будет обсужден более подробно в дальнейшем. Ток смещения IB может быть определен как Уравнение (7) может быть преобразовано путем замены напряжениями базы-эмиттера транзисторов Q1 и Q2 из уравнений (2) и (3),следующим образом: Если токами базы всех транзисторов пренебрегают, то ток через источник напряжения 106 может быть рассчитан следующим образом Ток коллектора любого транзистора равен произведению тока базы и коэффициента усиления потоку . Коэффициент усиления по току отличается для разных транзисторов и обычно находится в диапазоне от 40 до 300. Токи базы транзисторов Q1, Q2, Q3, и Q4, следовательно,малы относительно соответствующих токов коллектора, так что в первом приближении токами базы можно пренебрегать. В этом случае,токи коллектора выходных транзисторов Q1 иQ2 могут рассматриваться как равные. Таким образом, ток покоя Iq может быть определен как Сравнение уравнений (14) и (15) показывает, что ток коллектора транзистора Q3 равен току коллектора транзистора Q4. Поэтому токиIc3 и Ic4 могу быть рассчитаны из уравнения (12) следующим образом: Ток покоя - постоянный холостой ток, текущий через выходные транзисторы (то есть, от коллектора эмиттеру транзистора Q1 и от эмиттера к коллектору транзистора Q2), когда никакой сигнал не поступает на вход выходного каскада 100. При подстановке определения (9) в уравнение (8) ток покоя может быть рассчитан как Уравнение (10) подразумевает, что ток покоя - есть функция напряжения источника напряжения V1 и размера выходного транзистора. Уравнение (10) также подразумевает, что ток покоя независим от размера управляющих транзисторов Q3 и Q4, и источников тока смещенияI1 и I2. Эта независимость обеспечивает существенную свободу при проектировании; размер управляющего транзистора и источники тока смещения могут выбираться независимо от выходных транзисторов, тока покоя и размера. Делением уравнения (10) на уравнение (16) обеспечивается следующее соотношения между током покоя и током коллектора Сравнение уравнений (7) и (11) показывает, что сумма напряжений базы-эмиттера выходного транзистора равна сумме напряжений базы-эмиттера управляющего транзистора. Поэтому отношение токов коллектора выходных транзисторов Q1 и Q2 к токам коллектора управляющих транзисторов Q3 и Q4 должно быть равно отношению соответствующих площадей эмиттера, которое явно указано в уравнении (17). Те же самые отношения между током покоя и током управления коллектора существуют в цепи, показанной на фиг. 5. В случае, соответствующем фиг. 5, ток коллектора управляющих транзисторов равен значениям тока источников смещения, I1 и I2. Если токи источников тока смещения I1 и I2 равны, то Ic3 = lc4 = IB. Однако изменение размера области эмиттера управляющего транзистора, "х", в цепи, изображенной на фиг. 5, вызвало бы изменение тока покояIq, Это связано с тем, что источники тока смещения связаны только с управляющими транзисторами. В случае, соответствующем изобра 13 женному на фиг. 8 варианту настоящего изобретения, то же самое изменение размера области эмиттера управляющего транзистора не изменило бы ток покоя Iq. Вместо этого, токи коллектора управляющих транзисторов Ic3 и Ic4 изменяются в соответствии с уравнением (17). "Ток разности" между током смещения и током коллектора управляющих транзисторов течет через источник напряжения 106. Ток через источник управляющего напряжения 106 может быть рассчитан подстановкой уравнения (16) в уравнение (14) следующим образом: Как описано выше, правильная работа настоящего изобретения зависит от того факта,что ток IV1, который течет через источник управляющего напряжения 106, может измениться. Таким образом, источник управляющего напряжения должен быть способен к поддержанию постоянного напряжения V1 при изменении тока IV1. Фиг. 9 иллюстрирует схематическое представление предпочтительной реализации источника управляющего напряжения 106,предназначенного для использования в схеме примера реализации, изображенной на фиг. 8. Транзисторы Q19, Q20 и резистор R формируют источник напряжения создающий напряжениеV1 между узлами А и В (см. фиг. 8 и 9), которое может регулироваться как функция значения сопротивления резистора R. Напряжение между узлами А и В относительно постоянно в широком диапазоне токов, протекающих через источник напряжения 106. Для описания этого примера реализации источника управляющего напряжения 106, в дополнение к примечаниям,приведенным в описании детального действия выходного каскада 100, приведены следующие примечания:VR - напряжение на резисторе R;IR - ток через резистор; и е - основание натурального логарифма, е = 2,718. Напряжение между узлами А и В, V(A-B),может быть рассчитано следующим образом: Уравнения (19) и (20) показывают, что напряжения базы-эмиттера прибавляются, а напряжение на резисторе - вычитается из полного значения V(A-B) так, что при увеличении тока коллектора, напряжение базы-эмиттера также повышается. Почти весь ток коллектора течет через резистор R. При увеличении тока коллектора напряжение на резисторе R также увеличивается. Так как напряжение на резисторе вычитается из напряжений базы-эмиттера, указанные напряжения стремятся компенсировать друг друга, что устанавливает напряжение на узлах А и В на относительно постоянном уровне. 14 В более точной форме, токи коллектора и ток через резистор могут быть определены следующим образом: где I - ток, вытекающий из узла А и протекающий через узел В. Подстановка уравнений (21), (22) и (23) в уравнение (20) дает следующее уравнение для напряжения между узлами А и В: Как указано выше, напряжения базыэмиттера и напряжение на резисторе имеют тенденцию компенсировать друг друга, в связи с чем существует специфическое значение тока,для которого компенсация является совершенной. Это специфическое значение тока может быть рассчитано путем приравнивания производной напряжения между узлами А и В по току тока к нулю. Подстановка выражения (24) для V(A-B) в уравнение (25) дает следующее результирующее уравнение: и обеспечивает решение (26) для тока I: где I0 - номинальный ток через источник управляющего напряжения, для которого компенсация напряжения является идеальной. Заменой I0 из уравнения (27) в уравнении (24) рассчитывается напряжение на узлах А и В, для которого компенсация является совершенной: Уравнение (28) может быть упрощено с учетом того, что вклад последнего логарифмического члена в круглых скобках является весьма малым. Учтем, чтоявляется много большим единицы (1), для примера, min = 10. Для токов в сотни мкА, согласно уравнению(27), значение сопротивления резистора R составляет порядка к. (103) или меньше. Порядок амплитуды токов насыщения транзистора, ISP(N),составляет 10-16. При использовании этих чисел в уравнении (28), могут быть рассчитаны первые и последние логарифмические выражения в круглых скобках. Значение первого выражения составляет приблизительно 27, а последнего приблизительно 0,1. Существует различие порядков величин первого и последнего логарифмических выражений. Поэтому, последнее лога 15 рифмическое выражение может быть проигнорировано. Также, при принятии во внимание свойств логарифмической функции, 1n (е) = 1,уравнение (28) может быть преобразовано в следующий вид: Указанное выше уравнение демонстрирует, что напряжение между узлами А и В может быть задано с помощью резистора R. Использование того же приближения, то есть, при пренебрежении влиянием токов базы, уравнение(24), которое описывает зависимость напряжения между узлами А и В относительно тока I,может быть упрощено следующим образом:V(A-B), определенного в соответствии с уравнением (30). Напряжение на источнике напряжения 106 сохраняется относительно постоянным,когда ток, проходящий через него, охватывает относительно широкий диапазон. Фиг. 11 и 12 показывают погрешность напряжения на источнике напряжения 106, когда ток изменяется на 50 и на 100%, соответственно. Цепь, изображенная на фиг. 8, включающая определенное выполнение источника напряжения, изображенного на фиг. 9, показана на фиг. 13. Источник управляющего напряжения 106 образован транзисторами Q5, Q6 и резистором R1. Площадь эмиттера транзисторов источника напряжения определена как у. При использовании вышеупомянутых допущений и обозначений напряжение между узлами А и В,определенное уравнением (30), может быть представлено следующим образом: При пренебрежении токами базы транзисторов Q5 и Q6 напряжение между узлами А и В в основном независимо от тока, текущего через источник напряжения, IV1, когда ток имеет следующее значение: где I0V1 - номинальный ток, для которого напряжение между узлами А и В является независимым от тока IV1. Напряжение между узлами А и В, для которого влияние тока I V1 минимально, рассчитывается путем подстановки уравнения (32) в уравнение (31): Ток покоя выходных транзисторов Q1 и Q2 оценен путем подстановки уравнения напряжения (31) в уравнение (10) следующим образом: 16 Ток покоя является функцией тока, текущего через источник напряжения, связанный с узлами А и В. Ток IV1, в экспоненциальной части уравнения (34), приводит к уменьшению тока покоя. Ток IV1, умноженный на показательную функцию, приводит к увеличению значения тока покоя. Таким образом, эти два значения в уравнении (34), стремятся компенсировать друг друга и устанавливают ток покоя на почти постоянном уровне. Ток Iq, как функция от IV1,имеет максимум, который может быть рассчитан, подстановкой уравнения (32) в уравнение(34), следующим образом: Фиг. 14 показывает диаграмму тока покоя,в соответствии с уравнением (34). Результирующая кривая имеет пик (то есть, максимальное значение), который может быть рассчитан с использованием уравнения (35). Следует отметить, что при изменении тока через источник напряжения в широком диапазоне ток покоя остается в основном постоянным, в пределах 5%. Для качественного сравнения варианта выполнения, показанного на фиг. 13 с вариантом выполнения, известным из предшествующего уровня техники, показанным на фиг. 5, ток покоя Iq может быть построен в зависимости от тока источников тока смещения. Ток источника тока смещения является суммой тока коллектора управляющего транзистора и тока через источник напряжения. В типовых вариантах выполнения, известных из уровня техники, значения токов источников тока смещения I1 и I2 равны или очень близки по величине. Поэтому, разумно предположить, что они точно равны. Согласно этому предположению, токи коллектора управляющих транзисторов также равны. Отношения между током покоя и токами коллектора управляющих транзисторов показаны в уравнении (17). При подстановке Iq из уравнения (34) в уравнение (17), ток коллектора управляющего транзистора Q3 может быть рассчитан следующим образом: Подстановка уравнения (38) в уравнение(36) дает результат, выраженный следующим уравнением: Уравнение (39) не имеет аналитического решения для IV1. Для подготовки диаграммы зависимости тока покоя Iq от тока смещения IB,уравнение (39) сначала решается в численном виде и затем IV1 подставляется в уравнение (34),для окончательного вычисления Iq. Для сравнения предпочтительного варианта выполнения,изображенного на фиг. 13 с вариантом выпол 17 нения, известным из уровня техники, изображенным на фиг. 5, ток покоя выходных транзисторов Q1 и Q2 с фиг. 5 также показан на фиг. 15, на которой дается сравнение тока Iq цепи,обозначенной на фиг. 5 позицией 152 и тока Iq цепи, обозначенной на фиг. 13 позицией 154. В случае предпочтительного варианта выполнения(показанного на фиг. 13) ток покоя остается в основном постоянным, в то время как в цепи,известной из уровня техники (показанной на фиг. 5) ток покоя увеличивается в линейной зависимости от тока смещения. Согласно уравнению (17), токи коллектора управляющих транзисторов линейно пропорциональны току покоя. Следовательно, ток коллектора управляющих транзисторов весьма постоянен при изменении тока смещения, и если ток смещения изменяется, дополнительный ток,который течет через источник управляющего напряжения 106 (связанный между узлами, А и В) линейно пропорционален току смещения. Эта зависимость показана на фиг. 16, которая представляет выходной ток источника тока смещения 202, напряжение источника управляющего напряжения 204 и ток через управляющие транзисторы 206 в зависимости от выходного тока источника тока смещения. Так как не существует аналитического решения для тока покоя как функции тока смещения, не может быть рассчитана чувствительность тока покоя к току смещения. Однако, учитывая линейное отношение тока смещения к току через источник напряжения, достаточно хорошее приближение может быть сделано при вычислении тока покоя через ток, протекающий через источник напряжения. 18 нений (35) и (42) в уравнение (34) ток покоя выражается следующей формулой: Отметим что, изменение на +/-30% тока источника напряжения изменяет ток покоя только на 5%. При подстановке уравнения (42) в уравнение (39) получим выражение для тока смещения: Ток смещения обычно определяется как максимальный выходной ток, деленный на минимальный коэффициент усиления по току выходных транзисторов. Таким образом, значение сопротивления резистора R1 может быть рассчитано из уравнения (46) следующим образом: Ток смещения должен быть больше или равен максимальному току базы выходных транзисторов. Поэтому уравнение (46) может быть представлено как: Окончательное решение уравнения (48) для отношения областей эмиттера транзисторов представляется в следующем виде:(40), дает следующую зависимость для чувствительности: Ток покоя становится не зависящим от тока через источник напряжения, когда чувствительность Iq к IV1 равняется нолю. Это происходит в случае, когда ток через источник напряжения имеет следующее значение: Уравнение (42) эквивалентно уравнению(27). Тот же самый результат был достигнут при решении задачи двумя различными путями: i) минимизация зависимости напряжения между узлами А и В от тока, текущего через источник напряжения, и ii) минимизация тока покоя от тока источника тока смещения. При подстановке уравнения (42) в уравнение (34) номинальная рабочая точка для выходных транзисторов была рассчитана, в соответствии с уравнением (35). При подстановке урав Учтем, в соответствии с уравнением (35),что сопротивление резистора R1 может быть выражено как функция номинального тока покоя следующим образом: Окончательное решение для области эмиттера "у" транзистора источника тока находится подстановкой уравнения (50) в уравнение (49): Площадь транзистора - предпочтительно целое число. Таким образом, площадь эмиттера транзисторов источника напряжения предпочтительно округлена до целого числа следующим образом (была прибавлена единица, так как функция целочисленного преобразования уменьшает исходное число): Так как установлен размер выходного транзистора, необходимо определить наиболее эффективный размер управляющего транзистора и транзистора источника напряжения. Полная область транзистора: При подстановке уравнения (51) в уравнение (53), площадь всей области может быть рассчитана как функция размеров управляющих и выходных транзисторов следующим образом: Согласно уравнению (54), минимальная площадь достигается, когда управляющий транзистор имеет минимальный размер, 1 х. Площадь транзистора, необходимая для цепи, изображенной на фиг. 5: При подстановке уравнения (17) в уравнение (55), и с учетом того обстоятельства, что на фиг. 5 управляющий ток коллектора равен току смещения, уравнение (55) будет выглядеть в следующем виде: Экономия площади при новой топологии выходного каскада равна: При подстановке формул (54) и (56) в уравнение (57), получаем следующую экономию площади: Изобретение может быть реализовано в других формах выполнения с сохранением смысла или существенных характеристик изобретения. Настоящие примеры реализации в связи с этим должны рассматриваться как иллюстрация, а не ограничение, пределы изобретения отражены в приложенных пунктах формулы изобретения в большей степени, чем в приведенном выше описании и все изменения,которые могут быть внесены в пределах и в диапазоне эквивалентности признаков формулы изобретения, также охватываются формулой изобретения. ФОРМУЛА ИЗОБРЕТЕНИЯ 1. Устройство для промежуточного преобразования и развязки источника сигнала от внешней нагрузки, содержащее входной вывод, предназначенный для подачи на него входного сигнала от указанного источника сигнала, выходной вывод,предназначенный для формирования на нем выходного сигнала, передаваемого на указанную внешнюю нагрузку и соответствующего входному сигналу, первый источник тока смещения, предна 003440 20 значенный для подачи первого эмиттерного тока на первый управляющий транзистор и первого тока смещения на первый выходной транзистор, и второй источник тока смещения, предназначенный для приема второго эмиттерного тока от второго управляющего транзистора и второго тока смещения от второго выходного транзистора, причем указанный входной сигнал обеспечивает смещение указанных первого управляющего транзистора и второго управляющего транзистора, а указанный выходной вывод электрически подсоединен к эмиттеру указанного первого выходного транзистора и эмиттеру указанного второго выходного транзистора, отличающееся тем, что оно содержит источник управляющего напряжения, предназначенный для формирования управляющего напряжения и электрически включенный между эмиттером первого управляющего транзистора и эмиттером второго управляющего транзистора, при этом устройство выполнено с возможностью обеспечения изменения указанных первого тока смещения и второго тока смещения в соответствии с заранее заданной функцией от указанного управляющего напряжения. 2. Устройство по п.1, отличающееся тем, что указанный первый управляющий транзистор содержит транзистор р-n-р-типа, указанный второй управляющий транзистор содержит транзистор n-рn-типа, указанный первый выходной транзистор содержит транзистор n-р-n-типа, и указанный второй выходной транзистор содержит транзистор р-nр-типа. 3. Устройство по п.1, отличающееся тем, что оно содержит источники напряжения, электрически включенные между коллектором указанного первого выходного транзистора и коллектором указанного второго выходного транзистора. 4. Устройство по п.1, отличающееся тем, что указанная заранее заданная функция содержит в основном экспоненциальное отношение. 5. Устройство по п.1, отличающееся тем, что оно выполнено с возможностью прохождения через указанные первый и второй выходные транзисторы токов покоя, которые в основном не зависят от указанных первого источника тока и второго источника тока. 6. Устройство по п.1, отличающееся тем, что источник управляющего напряжения содержит резистор, транзистор р-n-р-типа, и транзистор n-р-nтипа, причем указанный резистор электрически включен между коллектором указанного транзистора р-n-р-типа и коллектором указанного транзистора n-р-n-типа, база указанного транзистора р-nр-типа электрически соединена с указанным коллектором транзистора n-р-n-типа, база указанного транзистора n-р-n-типа электрически соединена с указанным коллектором транзистора р-n-р-типа,эмиттер указанного транзистора р-n-р-типа электрически соединен с указанным эмиттером первого управляющего транзистора, а эмиттер указанного транзистора n-р-n-типа электрически соединен с 21 указанным эмиттером второго управляющего транзистора. 7. Устройство для промежуточного преобразования и развязки источника сигнала от внешней нагрузки, содержащее входной вывод, предназначенный для подачи на него входного сигнала от источника сигнала, и выходной вывод, предназначенный для формирования на нем выходного сигнала, передаваемого на внешнюю нагрузку, и снабженное выходным каскадом, содержащим первый транзистор n-р-n-типа с первым током покоя коллектора и первый транзистор р-n-р-типа со вторым током покоя коллектора, входным каскадом,содержащим второй транзистор р-n-р-типа, второй транзистор n-р-n-типа, первый источник тока и второй источник тока, причем эмиттер первого транзистора n-р-n-типа электрически соединен с эмиттером первого транзистора р-n-р-типа, коллектор первого транзистора n-р-n-типа соединен с первым источником напряжения, а коллектор первого транзистора р-n-р-типа соединен со вторым источником напряжения, эмиттер второго транзистора р-n-ртипа электрически соединен с первым выходным выводом источника тока и с базой первого транзистора n-р-n-типа, коллектор второго транзистора рn-р-типа электрически соединен с указанным вторым источником напряжения, база второго транзистора p-n-р-типа электрически соединена с указанным входным выводом, а входной вывод первого источника тока электрически соединен с первым источником напряжения, эмиттер второго транзистора n-р-n-типа электрически соединен с указанным входным выводом второго источника тока и с базой указанного первого транзистора р-n-р-типа,коллектор второго транзистора n-р-n-типа, электрически соединен с указанным первым источником напряжения питания, база второго транзистора n-рn-типа электрически соединена с указанным входным выводом, а выход второго источника тока электрически соединен с указанным вторым источником напряжения, отличающееся тем, что оно содержит источник управляющего напряжения,предназначенный для формирования управляющего напряжения и имеющий положительный вывод и отрицательный вывод, причем указанный положительный вывод электрически соединен с базой указанного первого транзистора n-р-n-типа, а указанный отрицательный вывод электрически соединен с базой указанного первого транзистора р-n-ртипа, при этом устройство выполнено с возможностью обеспечения изменения указанного первого тока покоя коллектора и указанного второго тока покоя коллектора в соответствии с заранее заданной функцией от указанного управляющего напряжения. 22 8. Устройство по п.7, отличающееся тем, что указанная заранее заданная функция является в основном экспоненциальной зависимостью. 9. Устройство по п.7, отличающееся тем, что указанный источник управляющего напряжения содержит резистор, третий транзистор р-n-р-типа и третий транзистор n-р-n-типа, причем указанный резистор электрически включен между коллектором указанного третьего транзистора р-n-р-типа и коллектором указанного третьего транзистора n-рn-типа, база указанного третьего транзистора р-n-ртипа электрически соединена с указанным коллектором третьего транзистора n-р-n-типа, база указанного третьего транзистора n-р-n-типа электрически соединена с указанным коллектором третьего транзистора р-n-р-типа, эмиттер указанного третьего транзистора р-n-р-типа электрически соединен с эмиттером указанного первого управляющего транзистора, а эмиттер указанного третьего транзистораn-р-n-типа электрически соединен с указанным эмиттером второго управляющего транзистора. 10. Буферный каскад для обеспечения промежуточного преобразования и развязки источника сигнала от внешней нагрузки, содержащий входной вывод, предназначенный для подачи на него входного сигнала от источника сигнала, и выходной вывод, предназначенный для формирования на нем выходного сигнала, передаваемого на указанную внешнюю нагрузку и соответствующего входному сигналу, причем буферный каскад снабжен входной секцией, содержащей, по крайней мере, два управляющих транзистора, каждый из которых выполнен с возможностью работы с предварительно заданным током смещения, выходной секцией,содержащей, по крайней мере, два выходных транзистора, каждый из которых выполнен с возможностью работы с заранее заданным током покоя, и источником напряжения, отличающийся тем, что источник напряжения подключен к входной и выходной секциям и выполнен с возможностью формирования токов покоя, протекающих через выходные транзисторы и в основном не зависящих от величин токов смещения, протекающих через управляющие транзисторы. 11. Буферный каскад по п.10, отличающийся тем, что он выполнен с возможностью регулирования напряжения от источника напряжения таким образом, что токи смещения через два управляющих транзистора имеют разветвление в различных соотношениях. 12. Буферный каскад по п.10, отличающийся тем, что он выполнен с возможностью формирования токов покоя выходных транзисторов, в основном не зависящими от размера области эмиттера каждого из управляющих.

МПК / Метки

МПК: H03F 3/18

Метки: преобразования, буферный, сигнала, каскад, нагрузки, источника, развязки, внешней, устройство(варианты)и, промежуточного, обеспечения

Код ссылки

<a href="https://eas.patents.su/15-3440-ustrojjstvovariantyi-bufernyjj-kaskad-dlya-obespecheniya-promezhutochnogo-preobrazovaniya-i-razvyazki-istochnika-signala-ot-vneshnejj-nagruzki.html" rel="bookmark" title="База патентов Евразийского Союза">Устройство(варианты)и буферный каскад для обеспечения промежуточного преобразования и развязки источника сигнала от внешней нагрузки</a>

Предыдущий патент: Способ доступа к ресурсам всемирной паутины

Следующий патент: Способ лечения гиперчувствительности дентина (варианты)

Случайный патент: Двухкомпонентные полиуретановые композиции и покрытия на водной основе